Lançado em janeiro de 2002, este circuito integrado da National Semiconductor é o único controlador chaveador da industria indicado para apicações em gerenciamento de energia em notebooks, displays e infraestrutura de informações com o mínimo de componentes externos. Projetado para implementar soluções em reguladores chaveados numa ampla faixa de tensões sem a necessidade de compenação ele é o mais fácil de usar de todos os componentes com topologia PFM (Pulse Frequency Modukation). Veja nesta artigo as características deste novo componente e alguns circuitos práticos de aplicação.

O LM3485 consiste num controlador chaveador regulado que permite ao projetista facilmente desenvolver reguladores do tipo "buck" (step down) com um mínimo de componentes externos para uma ampla faixa de aplicações.

O uso de um esquema histerético de controle proporciona um projeto simples sem a necessidade de loops de controle mantendo a estabilidade e assim reduzindo a necessidade de muitos componentes externos.

A arquitetura PFET também contribui para a redução do número de componentes externos e uma menor queda de tensão.

A proteção contra a ultrapassagem do limite de corrente é feita medindo-se a tensão através do PFET (Rdson) o que elimina a necessidade da solução tradicional de alto custo que faz uso de um resistor de sensoriamento em série com o FET. O limite de corrente pode então ser facilmente ajustado possibilitando ao projetista obter faixas diferentes de correntes e custos.

Destaques:

Metodologia de controle fácil de usar

Não há necessidade de loop de compensação

Faixa de tensões de entrada de 4,5 a 35 V

Faixa de tensões ajustável entre 1,242 V e Vin

Alta eficiência (93%)

Ciclo ativo 100 %

Freqüência de operação máxima maior que 1 MHz

Proteção para limite de corrente

Invólucro MSOP-9

Aplicações:

Set-Top Box

DSL/Modem por Cabo

PC/IA

Auto PC

Monitor TFT

Equipamentos alimentados por bateria

Sistemas distribuídos de energia

Sempre Alimentados (Always On Power)

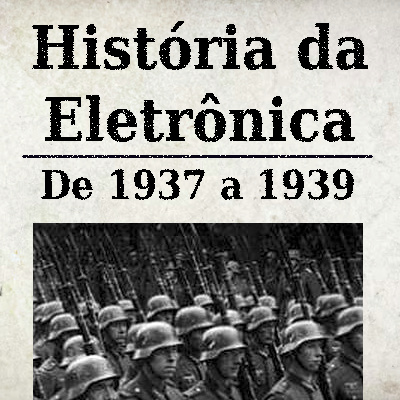

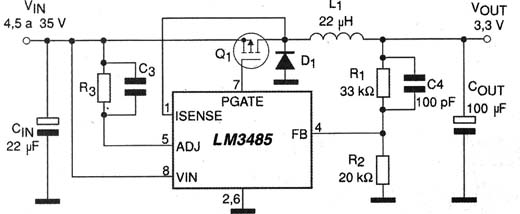

Na figura 1 temos uma aplicação típica do LM3485 onde, com uma entrada de 4,5 a 35 V obtemos uma saída constante de 3,3 V e corrente que depende do Power MOSFET usado.

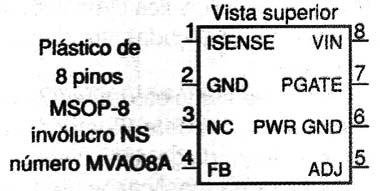

Na figura 2 temos o invólucro básico MSOP-8 usado para este componente.

Descrição dos pinos:

| Nome do Pino | Número do pino | Descrição |

| ISENSE | 1 | Entrada do sensoriamento de corrente. Este pino deve ser conectado ao dreno do PFET externo |

| GND | 2 | Terra de sinal |

| NC | 3 | Sem conexão |

| FB | 4 | Entrada de Feedback. Ligue o FB ao divisor de tensão resistivo entre a saída e terra para ajustar a tensão de saída. |

| ADJ | 5 | Ajuste do limiar do limiote de corrente. É conectado a uma fconte de corrente interna de 5,5 uA. Um resistor é ligado entre este pino e a entrada de alimentação. A tensão sobre este resistor é comparada com Vds do PFET externa para determinar quando uma condição de sobrecorrente ocorre. |

| PWR GND | 6 | Terra de potência |

| PGATE | 7 | Saída para a comporta do PFET externo. O sinal neste ponto oscila entre Vin e Vin-5 V. |

| VIN | 8 | Entrada de alimentação |

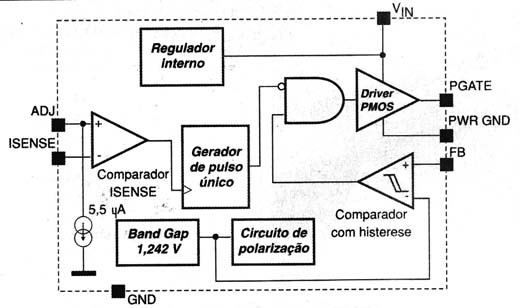

Na figura 3 temos um diagrama de blocos que representa as funções internas do LM3485.

O LM3485 é um controlador DC-DC do tipo buck (step-down ou redutor) que usa um esquema de controle histerético.

Nele, o comparador é projetado para ter uma histerese de aproximadamente 10 mV.

Assim, em resposta à tensão no pino FB, a saída de comporta para o Power MOSFET (pino PGATE) comuta o transistor de potência, ligando-o e desligando-o.

Quando a corrente no indutor é muito alta, o circuito limitador de corrente é ativado e desliga o PFET por aproximadamente 9 us.

O controle histerético não proporciona um oscilador interno.

A freqüência de chaveamento depende dos componentes externos e das condições de operação.

A freqüência de operação diminui com pequenas cargas resultando assim numa eficiência excelente quando comparada com outras estruturas.

Apenas dois resistores externos são usados para facilmente programar a tensão de saída.

A tensão de saída pode ser programa na faixa de valores compreendida entre 1,242 V e Vin (tensão de entrada).

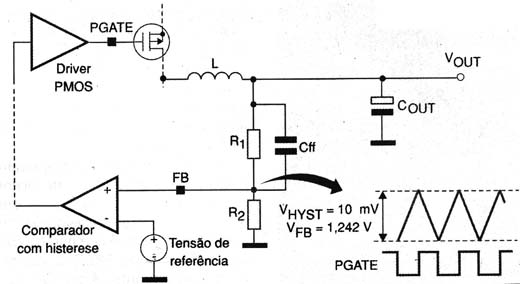

Vamos analisar melhor o funcionamento do Circuito de Controle Histerético, que é um dos destaques deste componente.

Circuito de Controle Histerético

O LM3485 usa um comparador baseado em um loop de tensão de controle.

A tensão de realimentação é comparada com uma referência de 1,242 V e uma histerese de 10 mV é agregada ao comparador para assegurar uma operação livre de ruído.

Quando a entrada FB para o comparador tem a tensão caindo para menos da tensão de referência, a saída do comparador vai para o nível baixo.

Isso faz com que o driver de saída PGATE vá ao nível baixo ligando o PFET.

Com o PFET conduzindo, a tensão de entrada passa por este componente e carrega o capacitor Cout e alimenta o circuito de saída através do indutor.

A corrente no indutor sobe linearmente e a tensão de saída aumenta. Quando a tensão FB alcança o limiar superior, que é a tensão interna de referência mais 10 mV, a saída do comparador passa do nível baixo para o nível alto e a saída PGATE responde desligando o PFET.

Quando o PFET desliga, a tensão no indutor inverte e o diodo de captura é polarizado no sentido direto fazendo com que a corrente através do indutor diminua linearmente.

Isso vai ocorrer até que a tensão de saída caia para a tensão de referência interna novamente e um novo ciclo tenha início.

Na figura 4 temos um diagrama simplificado deste setor do circuito com as formas de onda principais.

O LM3485 opera no modo de condução descontínuo com correntes pequenas de carga ou modo contínuo de condução com cargas de maiores correntes.

No modo descontinuo de condução, a corrente através do indutor parte de zero e aumenta até o valor de pico e então decai novamente até zero.

O ciclo seguinte começa quando FB alcança a tensão interna. Até então a corrente no indutor permanece nula.

A freqüência de operação é menor e as perdas se reduzem. No modo de condução contínuo, a corrente sempre circula através do indutor e nunca cai até zero.

A tensão de saída (Vout) pode ser programa por dois resistores externos calculados pela seguinte fórmula:

Vout = 1,242 (R1 + R2)/R2

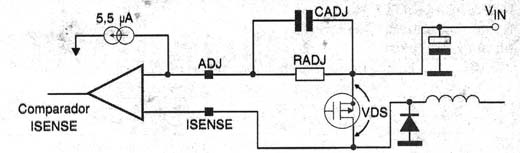

Operação do Limitador de Corrente

O LM3485 possui um limitador de corrente que opera ciclo a ciclo. A corrente é sensoriada através de Vds do PFET ou então através de um resistor adicional de sensoriamento.

Quando o limite de corrente é alcançado o LM3485 desliga o transistor PFET externo por um período de 9 us.

O limite de corrente é ajustado por um resistor externo (Radj).

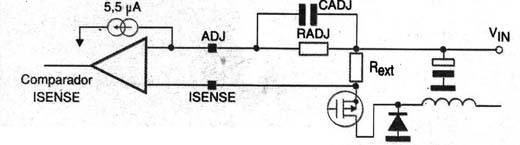

O circuito limitador de corrente é composto do comparador ISENSE e um gerador de pulso único, conforme mostra a figura 5.

A entrada positiva do comparador ISENSE é o pino ADJ. Um dreno de corrente interno de 5,5 uA cria uma tensão sobre o resistor externo Radj.

Esta tensão é comparada com a tensão através do PFET ou resistor de sensoriamento. A tensão ADJ pode ser calculada pela seguinte fórmula:

Vadj = Vin - (Radj x 5,5 uA)

A entrada negativa do comparador ISENSE é o pino ISENSE que deve ser conectado ao dreno do transistor PFET externo.

A corrente no indutor é determinada pelo sensoriamento de Vds, podendo ser calculada pela seguinte fórmula:

V isense = Vin - (Rdson x Iind.pico) = Vin - Vds

O limite de corrente é ativado quando a tensão no pino ISENSE supera a tensão no pino ADJ.

O comparador ISENSE dispara o pulso único de 9 us forçando o PFET a desligar. O driver liga novamente o PFET depois deste tempo.

Se a corrente não foi reduzida para menos do valor ajustado, o ciclo vai se repetir continuamente.

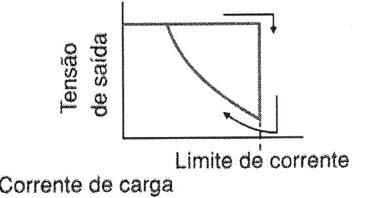

Durante a condição de limitação de corrente, a tensão de saída vai cair significantemente assim como a freqüência de operação.

Quando a corrente de carga for reduzida, a saída vai retornar à tensão programada.

Entretanto, deve ser levado em conta que existe um fenômeno de fold back inerente a esta arquitetura de limitação de corrente, conforme mostra a figura 6.

Circuito de Partida

O circuito limitador de corrente está ativo durante a partida. Durante o período de partida, o PFET deve estar ligado até que o limite de corrente ou o ponto de computação do comparador seja alcançado.

Se o comparador limitador de corrente é comutado antes então a característica de fold back deve ser levada em conta no projeto.

Partida à plena carga vai exigir um ajuste do limite de corrente maior do que na operação normal depois da partida.

Um problema ao se selecionar um limite de corrente maior é a corrente de surto durante a partida.

A adição de uma capacitância (Cadj) em paralelo com Radj resulta numa partida suave e Radj cria um circuito RC de tempo forçando o limitador de corrente a ser ativado com correntes maiores.

Desta forma, a rampa da tensão de saída será mais suave.

O Cadj também filtra ruído indesejável de tal forma que o comparador ISENSE não seja disparado acidentalmente.

Um valor entre 100 pF e 1 nF é recomendado para a maioria das aplicações.

Estes valores pequenos terão pouco ou nenhum efeito sobre a partida suave.

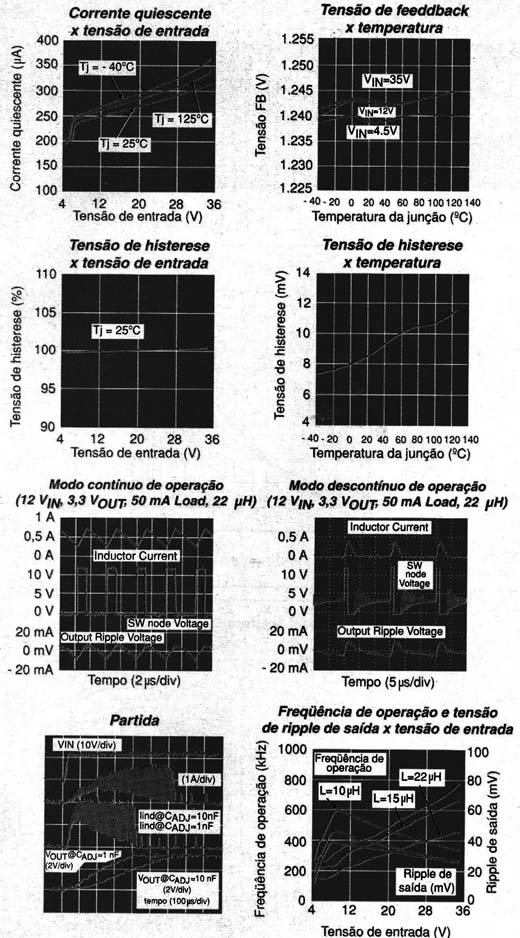

As curvas que se seguem na figura 7 mostram o desempenho deste componente em diversas condições.

Resistor Externo de Sensoriamento

O Vds de um PFET tende a variar sensivelmente com a temperatura. Isso pode resultar numa variação equivalente do limite de corrente.

Para melhorar a precisão do limitador de corrente um resistor externo de sensoriamento pode ser conectado entre o Vin e a fonte (s) do PFET, conforme mostra a figura 8.

Informações Adicionais

Datasheet completo deste componente, contendo curvas de desempenho, descrição detalhada e exemplo de projeto pode ser obtido no site da National Semiconductor em inglês, no formato PDF. O endereço é: http://www.national.com/pf/LM/LM3485.html

Obs.: A National é agora empresa do grupo Texas Instruments.