Circuitos de amostragem e retenção (Sample and Hold) são usados em aquisição de dados no interfaceamento de dispositivos sensores com PCs, e em outras aplicações importantes que envolvam o armazenamento de informações na forma analógica por um curto intervalo de tempo. Neste artigo, adaptado do Linear Application Handbook da National Semiconductor abordamos algumas soluções interessantes, com circuitos práticos, para o problema da amostragem e retenção.(1997)

Existem aplicações em que as características de componentes convencionais usados na amostragem e retenção não são suficientes para atender as condições de funcionamento. É o caso de circuitos em que se necessita de um tempo de manutenção maior, transferência rápida de dados, etc.

Os circuitos que apresentamos a seguir possuem características que podem ser muito interessantes para o projetista.

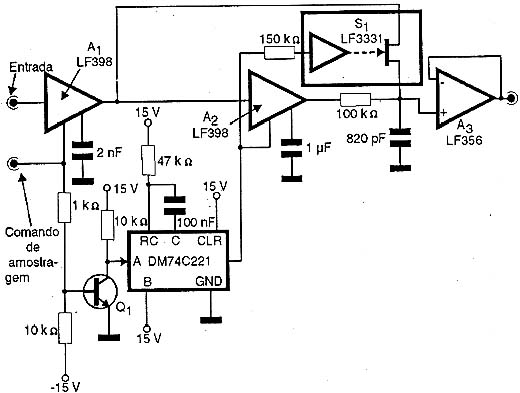

TEMPO DE RETENÇÃO ESTENDIDO

O circuito apresentado na figura 1 possui um tempo de retenção ampliado o que é conseguido pelo "empilhamento" de dois circuitos de amostragem e retenção numa espécie de cadeia.

O tempo rápido de aquisição por um circuito "feed forward". Quando um comando de amostragem é aplicado ao circuito, A1 lê o sinal rapidamente já que o valor do capacitor de 0,00 µF deste circuito é muito pequeno e portanto sua carga não demora. O comando de amostragem também é usado para disparar o DM74C221 (one-shot) que comuta a chave FET S1.

Neste momento a saída é ligada imediatamente ao buffer de saída A3. Durante este intervalo de tempo a saída do monoestável (one-shot) estará no nível alto, e A2 adquire o valor da saída de A1. Quando a saída do monoestável cai, S1 abre, desligando a saída de A1 da entrada de A3 e a saída do circuito não muda em relação ao valor amostrado.

Este circuito pode amostrar uma tensão de 10V em 10 us com 0,01% e tem uma taxa de perda de amostragem de 30 uV/segundo.

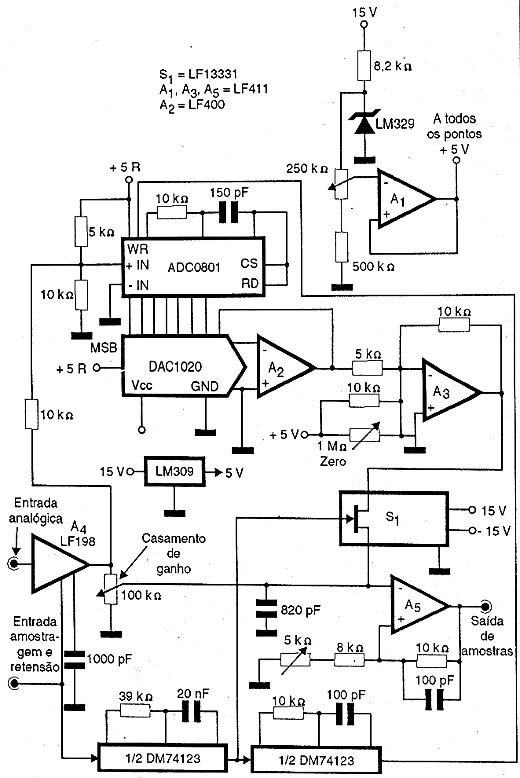

AMOSTRAGEM E RETENÇÃO INFINITA

Na figura 2 temos um circuito que estende o tempo de retenção ao infinito, com um tempo de amostragem de 10 us.

Uma vez que o sinal seja amostrado, não ocorre qualquer variação na tensão de saída, qualquer que seja o intervalo de tempo considerado.

Neste circuito o comando de amostragem é também usado para disparar dois monoestáveis DM74123. O primeiro monoestável é usado para polarizar a chave com FET, mantendo-a desligada (OFF) quando no nível baixo. O segundo monoestável envia um pulso ao conversor analógico/digital ADC0801 que faz então a conversão da saída de A4 para a forma digital. O DAC1020, em combinação com A2 e A3 converte a saída do conversor A/D de volta a forma analógica (tensão). O processo todo de conversão A/D/A leva apenas 100 us. Quando o tempo do monoestável termina, sua saída vai ao nível alto, fechando a chave com FET.

Esta ação conecta efetivamente a saída de A3 à entrada de A5 enquanto que a saída de A4 é desconectada. Desta forma, a saída do circuito vai permanecer no nível DC que originalmente determinou a amostragem feita por A4.

Como valor obtido na amostragem tem uma retenção na forma digital, nenhum erro por queda gradual da tensão em capacitores é introduzido. A precisão dos resistores é que vão determinar a precisão do circuito.

Com os valores indicados o circuito pode trabalhar com tensões de entrada na faixa de -10 a +10 V

AMOSTRAGEM E RETENÇÃO DE ALTA VELOCIDADE

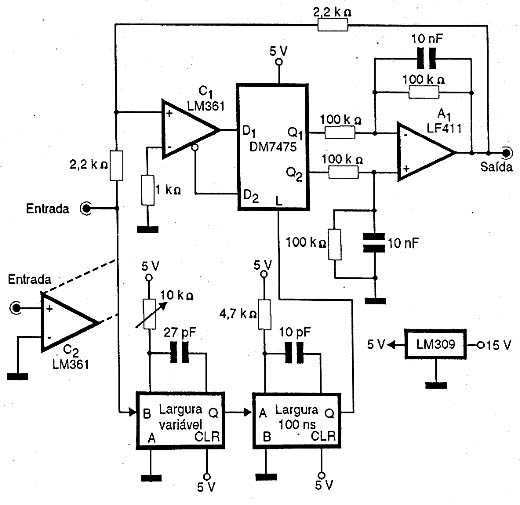

Um outro tipo de circuito de amostragem e retenção exigido em muitas aplicações práticas é o de alta velocidade. Se bem que circuitos convencionais de amostragem e retenção possam ser elaborados para tempos muito curtos de aquisição, eles são complexos e caros. na figura 3 temos então a solução dada pela National para este tipo de circuito, quando o sinal amostrado é repetitivo.

Neste circuito um comparador de tensão muito rápido e um "latch" ou trava digital são colocados antes de um integrador diferencial.

Um elo de realimentação é usado de modo a fechar o circuito entre estes elementos. cada vez que um impulso de entrada é aplicado, o latch DM7475 abre por 100 ns. Se a tensão de erro no Lm361 for positiva A1 vai aplicar corrente neste ponto. Se a tensão de erro for negativa, ocorre o inverso. Depois de um certo número de pulsos de entrada, A1 estará num nível DC que será equivalente ao valor amostrado na janela de 100 ns. Note que o intervalo de tempo do monoestável A é variável, permitindo que o pulso de amostragem do monoestável B seja colocado no ponto exato que se deseja da forma de onda do sinal de entrada.

AMOSTRAGEM E RETENÇÃO EM PASSO REDUZIDO

Uma outra área de interesse onde técnicas especiais podem significar melhoramentos no desempenho de um circuito é a minimização do passo de retenção.

Quando chaves padronizadas de amostragem e retenção são usadas, um pico de grande intensidade pode ocorrer. Isto é denominado passo de manutenção e normalmente é devido a capacitâncias internas das chaves com FETs usados nos circuitos.

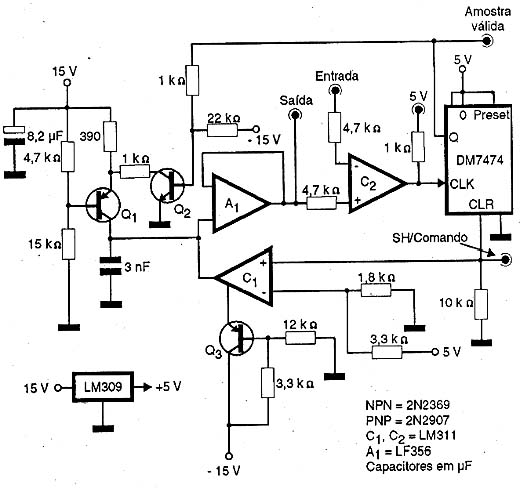

Na figura 4 temos um circuito que reduz enormemente este efeito, usando uma variação pouco comum do processo de amostragem e retenção.

Neste circuito a amostragem tem início quando o comando de amostragem e retenção vai ao nível baixo. Esta ação arma o flip-flop DM7474. Ao mesmo tempo, a saída de C1 leva o emissor de Q3 a um potencial de -12V . Quando o pulso de amostragem retorna ao nível alto, a saída de C1 vai ao nível alto e o capacitor de 0,003 µF é linearmente carregado pela fonte de corrente constante com base em Q1.

A rampa obtida no processo é seguida por A1 que acompanha C2. Quando o valor atingido pela rampa se torna igual a tensão de entrada do circuito, a saída de C2 vai ao nível alto, fazendo com que o flip-flop comute passando sua saída ao nível alto. Isto faz com que Q2 comute, cortando a fonte de corrente constante formada por Q1. O resultado final é parada da subida da tensão de rampa que então permanece no mesmo potencial da tensão de entrada.