11.1 - O que é um registrador de deslocamento

Um registrador de deslocamento ou "shift-register", como também é chamado pelo termo em inglês, consiste num conjunto de flip-flops que podem ser interligados de diversas formas como, por exemplo, as mostradas na figura 82.

Estes circuitos podem deslocar uma informação (bit) aplicado na entrada de uma posição, a cada pulso de clock. Por exemplo, o bit 1 aplicado na entrada aparece na saída do primeiro flip-flop no primeiro pulso de clock, depois desloca-se aparecendo na saída do segundo flip-flop, no segundo pulso de clock, e assim por diante, até aparecer na saída do final da sequência, conforme mostra a figura 2.

Na configuração mostrada na figura 1 (a), cada flip-flop tipo D tem sua saída conectada à entrada do flip-flop seguinte, e todos eles são controlados pelo mesmo sinal de CLOCK.

Para entender como funciona esse circuito vamos partir da situação inicial em que todos eles estejam desativados ou com suas saídas Q no nível baixo.

Inicialmente, vamos aplicar à entrada de dados um nível alto (1). Conforme podemos ver, esta entrada é feita pela entrada J do primeiro flip-flop (FF1).

Com a chegada do pulso de clock a este flip-flop, ele muda de estado e com isso "armazena" o pulso aplicado à entrada, o qual aparece em sua saída, depois de um curto intervalo de tempo. Veja que este sinal é armazenado com o flanco positivo do sinal de clock, quando então o nível alto deve estar presente na entrada do flip-flop.

O intervalo de tempo que decorre entre a aplicação do sinal na entrada de dados e seu aparecimento na saída do flip-flop é da ordem de alguns nanossegundos nos integrados das famílias lógicas comuns, mas é importante que em muitas aplicações mais rápidas ele seja levado em conta.

Para aplicações muito rápidas, dá-se preferência ao uso dos circuitos integrados de algumas subfamílias TTL.

No próximo pulso de clock, ocorre algo interessante: a entrada do primeiro flip-flop já não tem mais o nível alto e, portanto, FF1 não muda de estado. No entanto, na saída de FF1 temos nível alto, e esta saída está ligada à entrada do segundo flip-flop (FF2).

Isso significa que, com a chegada do segundo pulso de clock, o nível lógico da saída do primeiro se transfere para a saída do segundo, depois, é claro, de um pequeno intervalo de tempo, conforme mostra a tabela abaixo.

Temos então que, o bit 1 aplicado na entrada, se "desloca" mais um pouco no circuito, passando para a saída do segundo flip-flop.

É claro que, se nessa segunda passagem, tivermos aplicado um novo nível 1 na entrada do circuito, ele ao mesmo tempo que o primeiro se transfere para o segundo flip-flop, o segundo se transfere para a saída do primeiro flip-flop, como mostra a figura 84.

Chegando agora um terceiro pulso de clock, teremos nova transferência e o nível alto ou bit 1 se transfere para a saída do flip-flop seguinte, ou seja, FF3.

Em outras palavras, a cada pulso de clock, os níveis existentes nas saídas dos flip-flops, sejam eles 0 ou 1, se transferem para o flip-flop seguinte.

Assim, supondo que apliquemos, em sequência, na entrada de um shift-register como o indicado os níveis 0101, teremos a seguinte sequência de condições de saída para os flip-flops de um shft-register que use 4 deles:

| Clock | Entrada | FF1 | FF2 | FF3 | FF4 |

| inicio | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 |

| 2 | 1 | 0 | 1 | 0 | 0 |

| 3 | 0 | 1 | 0 | 1 | 0 |

| 4 | 0 | 0 | 1 | 0 | 1 |

Veja então que no quinto pulso de clock, o primeiro pulso de clock, o primeiro nível lógico, aparece na saída do último flip-flop (FF4) e que, se lermos a saída dos flip-flops, teremos registrado os níveis aplicados na entrada: 0101.

O leitor já deve ter percebido que aplicando um dado binário num shift-register, depois do número apropriado de pulsos de clock, que corresponde ao número de bits que ele contém, ele pode armazenar este dado.

Para retirar o dado em sequência, basta continuar aplicando pulsos de clock ao circuito, conforme a seguinte tabela:

| clock | FF1 | FF2 | FF3 | FF4 | saída |

| início (4) | 0 | 1 | 0 | 1 | 1 |

| 5 | 0 | 0 | 1 | 0 | 0 |

| 6 | 0 | 0 | 0 | 1 | 1 |

| 7 | 0 | 0 | 0 | 0 | 0 |

A figura 85 mostra o que ocorre em pormenores:

Perceba que, para armazenar um dado de 4 bits num registrador, devemos aplicar 4 pulsos de clock e para ler em sequência, mais 4 pulsos de clock.

Para "apagar" os dados registrados num shift-register, todos de uma vez, como o indicado, basta aplicar um pulso na entrada CLEAR.

Todos os flip-flops terão suas saídas levadas ao nível baixo ou 0.

11.2 – Tipos de registradores de deslocamento

Dependendo da maneira como a informação entra e como ela pode ser obtida num registrador de deslocamento, podemos ter diversas configurações que nos levam a diversos tipos de circuitos.

Assim, existem circuitos em que temos uma entrada serial ou duas, e também podemos ter uma ou duas linhas de saída.

A seguir, veremos os principais tipos como suas denominações.

SISO - Serial-in/serial out

No exemplo que tomamos, os dados foram aplicados à entrada do registrador na forma de níveis lógicos um atrás do outro, acompanhando o sinal de clock. Dizemos que este registrador opera com a carga de dados "serial" ou em série. Em outras palavras este circuito tem entrada serial ou serial-in.

Exatamente como ocorre com a porta serial de um computador, os dados são "enfileirados", entrando um após outro, sendo então armazenados em flip-flops, conforme mostra o circuito da figura 86.

PISO - Parallel-in/Serial out

No entanto, existe uma segunda possibilidade de operação para os shift-registers, que é a de operar com a entrada de dados em paralelo e sair com estes mesmos dados em série. Dizemos que se trata de um shift-register com entrada paralela e saída serial.

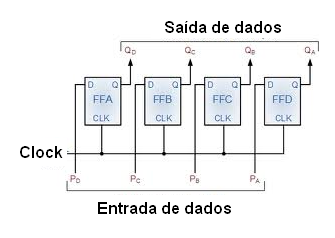

Na figura 87 temos um diagrama que usa 4 flip-flops tipo D e que tem entrada de dados paralela e saída serial.

Analisemos como ele funciona:

Os dados são colocados ao mesmo tempo na entrada, pois ela opera em paralelo. Por exemplo, se vamos armazenar o dado 0110 estes dados são aplicados ao mesmo tempo nas entradas correspondentes (S) dos flip-flops.

No primeiro pulso de clock, os flip-flops "armazenam" estes dados. Assim, os flip-flops que possuem nível 1 em sua entrada S passam esse nível a saída (FF2, FF3). Por outro lado, os que possuem nível 0 na sua entrada, mantém este nível na saída (FF1 e FF4).

Isso significa que após o pulso de clock, as saídas dos flip-flops apresentarão os níveis 0110.

SIPO - serial-In/Parallel-out

Da mesma forma, como mostra a figura 88, podemos carregar os dados em série e fazer sua leitura em paralelo.

Os registradores que operam desta forma podem ser também denominados conversores série-paralelo ou paralelo-série, conforme o modo de funcionamento.

Esse tipo de registrador é muito importante na transmissão de dados através de meios físicos (transmissão serial), já que ele pode fazer sua conversão para a forma digital normal de dados que chegam serialmente, transmitidos por um modem.

PIPO - Parallel-in/Parallel-out

Estes são circuitos em que os dados são carregados ao mesmo tempo (paralelos), e depois lidos ao mesmo pelo tempo pelas saídas dos flip-flops, conforme mostra a figura 89.

Os registradores de deslocamento são ainda classificados conforme a direção em que os dados podem ser deslocados.

Dizemos que se trata do tipo Shift-Right quando os dados são deslocados para a direita e que se trata de um tipo Shift-Left quando os dados são deslocados somente para a esquerda. (right = direita, left = esquerda)

Existem ainda os tipos bidirecionais, como o mostrado na figura 90, em que os dados podem ser deslocados nas duas direções. Este é um registrador do tipo SISO.

Veja que o sentido de deslocamento é determinado por uma entrada que atua sobre portas que modificam o ponto de aplicação dos sinais em cada flip-flop, exatamente como estudamos nos contadores up e down das lições anteriores.

Com a aplicação de um nível lógico conveniente na entrada LEFT/RIGHT, podemos determinar o sentido de deslocamento dos dados no circuito.

11.3 – Operando com binários

Conforme o leitor já percebeu, os registradores de deslocamento podem memorizar números binários, recebendo-os em série ou paralelo e entregando-os depois em série ou paralelo.

Nos computadores, calculadoras, modems, sistemas de transmissão de dados e muitos outros equipamentos digitais esta configuração é bastante usada, tanto na conversão de dados de portas, como nas próprias memórias, e outros circuitos internos.

É interessante observar que na configuração que tomamos como exemplo, em que são usados 4 flip-flops, os bits armazenados seguem uma determinada ordem.

Assim, quando representamos o número 5 (0101), cada um dos bits tem um valor relativo, que depende da sua posição no número, ou quantidade representada, conforme já estudamos em lições anteriores.

| bit | 0 | 1 | 0 | 1 | |

| valor | 8 | 4 | 2 | 1 | |

| no dado | 8x0 | 4x1 | 2x0 | 1x1 | |

| total | 0 + | 4 + | 0 + | 1 = | 5 |

| MSB | LSB | ||||

MSB significa bit mais significativo, (Most Significant Bit), ou seja, de maior peso, enquanto que LSB significa bit menos significativo ou de menor peso (Least Significant Bit, do inglês).

(Estamos trabalhando com dados de 4 bits, e não 8 como é comum nos computadores, obtendo-se assim o "byte", para maior facilidade de entendimento - o grupo de 4 bits também é chamado "nibble")

Ligando então 4 flip-flops de modo a se obter um shift-register, como mostra a figura 91, entrando com os dados de tal forma que o bit menos significativo seja o primeiro (LSB) ele vai aparecer, depois de 4 pulsos de clock na saída do último flip-flop.

Da mesma forma, se o shift-register for carregado em paralelo, o bit menos significativo (LSB) deve entrar no último flip-flop, de modo que na leitura ele seja o primeiro a sair.

Nos projetos que usam shift-register, a ordem de entrada e saída dos bits é muito importante para se obter o funcionamento correto do aparelho.

11.4 – Shift-registers ou registradores de deslocamento integrados

Podemos encontrar registradores de deslocamento tanto nas famílias TTL como CMOS. Os mesmos tipos encontrados na família TTL normal também podem ser encontrados nas diversas subfamílias.

Evidentemente, a velocidade máxima de operação de cada tipo depende da família a que ele pertence.

Vamos dar alguns exemplos de circuitos integrados comuns que podem ser usados em projetos, analisando suas principais características.

7495 - SHIFT REGISTER DE 4 BITS

(Da esquerda para a direita - entrada e saída em paralelo)

Este circuito integrado TTL pode operar de duas formas: Shift ou Load. Na figura 92 temos sua pinagem.

Para operar no modo shift, basta colocar a entrada MODE no nível baixo. Uma transição do nível alto para o nível baixo na entrada de clock SRT movimenta os dados de uma etapa para a direita.

Uma transição do nível alto para o baixo na entrada SLT movimenta o dado no sentido inverso. É interessante observar que este circuito usa dois clocks, um para movimentar os dados para a direita e outro para a esquerda.

No modo Load, esta entrada deve ir ao nível alto, e a informação carregada nas entradas LA, LB, LC e LD entram no circuito na transição do nível alto para o baixo da entrada de comando na entrada shift-left (SLT).

A frequência máxima de operação de um 7495 standard é de 36 MHz. Velocidades maiores de operação podem ser conseguidas com os tipos LS.

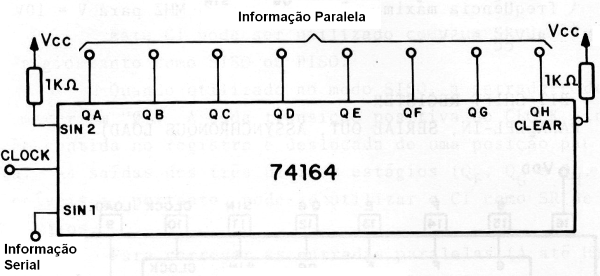

74164 - SHIFT REGISTER DE 8 BITS

(Entrada serial, saída paralela)

Na figura 93 temos a pinagem deste shift-register TTL.

Este circuito integrado pode ser usado na configuração de serial in/serial out ou ainda serial in/parallel-out, ou seja, entrada e saída de dados em série, ou entrada de dados em série e saída em paralelo.

Na operação normal, uma das saídas seriais é mantida no nível alto e os dados são aplicados à segunda entrada serial. A entrada Clear é mantida no nível alto e, a cada pulso do nível baixo para o alto do clock os dados movem-se de um estágio no circuito.

O conteúdo do shift-register pode ser zerado a qualquer momento, levando-se a entrada clear por um instante ao nível baixo. A frequência máxima de operação deste circuito na série Standard é de 36 MHz.

Os componentes equivalentes de algumas subfamílias podem chegar a frequências bem maiores de operação.

74165 - SHIFT REGISTER DE 8 BITS

(Entrada Paralela, saída serial)

Este circuito integrado TTL contém um shift-register de 8 bits com entrada paralela e saída de dados serial. A pinagem é mostrada na figura 94.

Para operação normal, EN deve ficar no nível baixo e LOAD no nível alto. Nessas condições os dados são deslocados de um estágio na transição positiva do sinal de clock.

Quando a entrada LOAD é levada ao nível baixo, o conteúdo das entradas de A até H é carregado no registrador.

Fazendo EM = 0 e LOAD = 1 os dados são deslocados de uma etapa no circuito a cada transição positiva do sinal de clock. A última etapa do circuito dispõe de um acesso para a saída complementar.

Para os circuitos integrados da série normal a frequência máxima de clock é 26 MHz e o consumo por unidade 42 mA.

Damos a seguir alguns registradores de deslocamento da família CMOS.

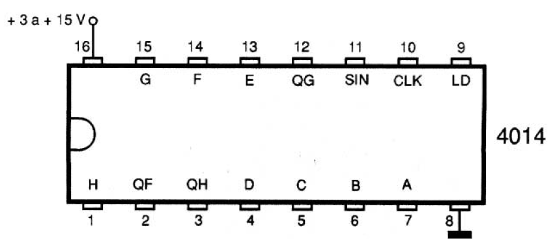

4014 - SHIFT REGISTER ESTÁTICO DE 8 BITS

(Entrada paralela e saída em série)

Este circuito integrado CMOS tem a pinagem mostrada na figura 95.

Um controle série/paralelo controla a entrada e habilita as etapas individuais de cada um dos 8 estágios. As saídas Q são disponíveis nos estágios 6, 7 e 8. Todas as saídas podem fornecer ou drenar a mesma intensidade de corrente.

Quando a entrada de controle paralelo/série está no nível baixo, os dados são deslocados pelo circuito a cada transição positiva do sinal de clock. Quando a entrada de controle está no nível alto, os dados são aplicados a cada etapa do shift-register com as transição positiva do clock.

A frequência máxima de operação deste tipo de circuito depende da tensão de alimentação. Para uma alimentação de 10 volts esta frequência é da ordem de 5 MHz caindo para 2,5 MHz com uma alimentação de 5 volts.

Na tabela abaixo as características elétricas desse CI:

|

Característica |

Condições (Vdd) |

Valor |

|

Corrente drenada/fornecida de saída (tip) |

5 V 10 V 15 V |

0,88 mA 2,25 mA 8,0 mA |

|

Frequência máxima de clock |

5 V 10 V 15 V |

4 MHz 12 MHz 16 MHz |

|

Corrente quiescente (max) |

5 V 10 V 15 V |

0,1 mA 0,2 mA 0,3 mA |

|

Faixa de tensões de alimentação |

3 V a 15 V |

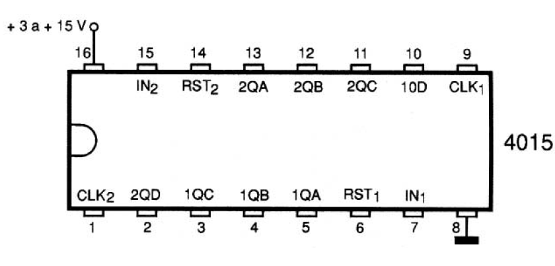

4015 - DOIS SHIFT REGISTERSS DE 4 BITS

(Entrada serial, Saída paralela)

A pinagem deste circuito fornecido em invólucro DIL de 16 pinos ‚ mostrada na figura 96.

Neste circuito integrado encontramos dois shift-registers que podem ser usados de modo independente.

Na operação normal, RST deve ser colocado no nível baixo. Levando esta entrada ao nível alto o circuito resseta o shift-register correspondente levando todas suas saídas ao nível lógico 0.

Os dados são deslocados a cada transição positiva do pulso de clock.

Na tabela damos as principais características elétricas desse CI:

|

Característica |

Condições (Vdd) |

Valor |

|

Corrente drenada/fornecida de saída (tip) |

5 V 10 V 15 V |

0,88 mA 2,25 mA 8,8 mA |

|

Frequência máxima de clock |

5 V 10 V 15 V |

3,5 MHz 8 MHz 11 MHz |

|

Corrente quiescente (max) |

5 V 10 V 15 V |

5 mA 10 mA 15 mA |

|

Faixa de tensões de alimentação |

3 V a 15 V |

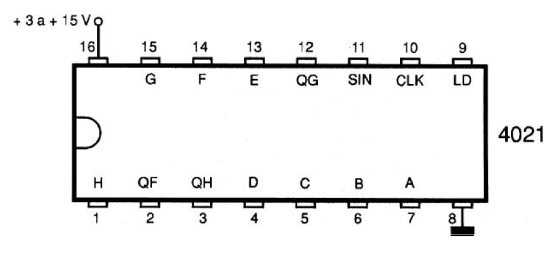

4021 - SHIFT REGISTER DE 8 BITS

(Parallel in, Serial out)

Este circuito integrado, cuja pinagem é mostrada na figura 97, é semelhante ao 4014.

A diferença está no fato de que a carga (LOAD) pode ser feita de forma assíncrona. Isso significa que esta entrada independe do sinal de clock.

Na tabela temos as principais características elétricas do 4021.

|

Característica |

Condições (Vdd) |

Valor |

|

Corrente drenada/fornecida de saída (tip) |

5 V 10 V 15 V |

0,88 mA 2,25 mA 8,8 mA |

|

Frequência máxima de clock |

5 V 10 V 15 V |

3,5 MHz 10 MHz 16 MHz |

|

Corrente quiescente (max) |

5 V 10 V 15 V |

0,1 mA 0,2 mA 0,3 mA |

|

Faixa de tensões de alimentação |

3 V a 15 V |

11.5 – Usando shift-registers

Existem muitas aplicações práticas para os shift-registers. A seguir, analisaremos algumas delas:

Conversão Série/Paralelo e Paralelo/Série

Uma das aplicações mais comuns dos registradores de deslocamento é a conversão de informações da forma paralela para serial e da forma serial para paralela.

Na figura 98 damos um exemplo de como podemos converter uma sequência de bits transmitidos em série por uma linha em um conjunto de saídas paralelas que correspondam exatamente a estes bits.

Este tipo de aplicação pode ser encontrada nos modems, e outros sistemas de transmissão de dados seriais, que recebem um fluxo de bits em uma única linha e que devem ser transferidos para uma saída paralela em 8 linhas, que é o modo de operação dos computadores.

Este circuito emprega um shift-register do tipo SIPO (Entrada Serial e Saída Paralela).

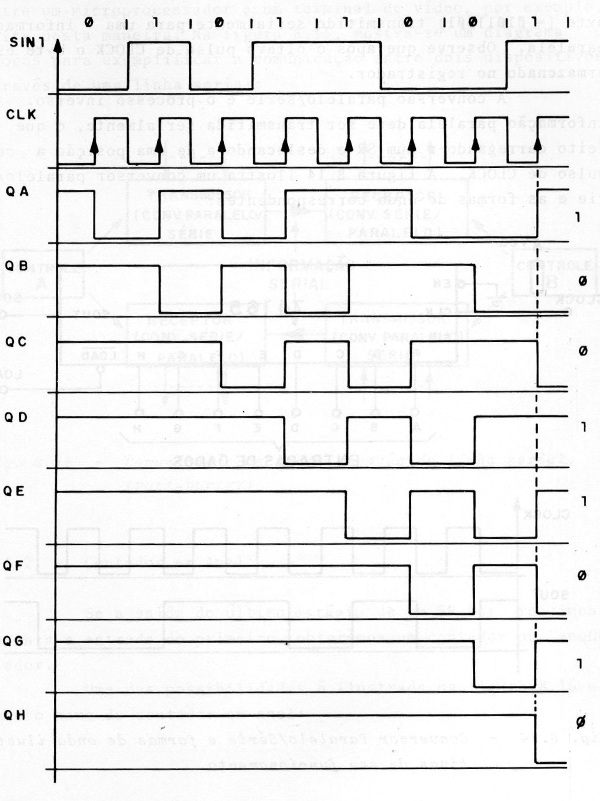

Vamos usar o gráfico de tempos da figura 99 para ilustrar como ele funciona e de que modo a sequência de dados aparece serialmente na sua saída.

Na primeira linha do gráfico de tempos temos a sequência de níveis lógicos que é aplicada à entrada do circuito e que corresponde justamente à informação serial que devemos tornar paralela.

Veja que dois bits 1 seguidos não possuem uma "separação", mas sim são distinguidos pelo tempo que corresponde a dois ciclos de clock.

Na segunda linha temos o sinal de clock que vai sincronizar a transferência desses sinais ao longo do registrador de deslocamento.

Nas linhas seguintes temos então a carga dos sinais que vão se deslocando pelo shift-register até que ao final do oitavo ciclo do clock o sinal estar presente em todas as saídas do circuito na forma paralela.

A transformação de dados da forma paralela para forma serial também é muito importante em aplicações digitais que envolvem informações na forma digital. Os dados das linhas paralelas do computador devem ser serializados para serem transmitidos por uma linha telefônica, por exemplo.

Podemos usa um shift-register como o 74165 para fazer isso. A figura 100 mostra o modo de ligação deste componente.

Os sinais são aplicados nas entradas de dados e, com um comando LOAD, eles são carregados no shift register. Depois disso, a cada pulso de clock os sinais são transferidos, bit por bit, para a saída.

A forma de sinais para uma sequência de dados 0101100 é mostrada na figura abaixo.

Contadores em anel

Outra aplicação importante para os registradores de deslocamento é o contador de anel ou "ring counter". Este tipo de circuito é obtido quando a saída do shift-register for reaplicada à sua entrada, conforme mostra a figura 101.

Neste circuito, carregando o primeiro estágio com o bit 1 e mantendo os demais com 0. Para isso é usada a linha INIT.

A cada pulso de clock que for aplicado ao circuito o bit 1 será deslocado de um estágio e quando atingir o último, será "realimentado" passando para o primeiro. Neste circuito, em cada instante, dependendo da quantidade de pulsos aplicado, o bit 1 estará presente em uma das saídas do circuito.

A tabela verdade para este tipo de circuito,com n flip-flops, é mostrada abaixo.

|

Pulso de Clock |

Q1 |

Q2 |

Q3 |

... |

Qn-1 |

Qn |

|

0 |

1 |

0 |

0 |

x |

0 |

0 |

|

1 |

0 |

1 |

0 |

x |

0 |

0 |

|

2 |

0 |

0 |

1 |

x |

0 |

0 |

|

... |

x |

x |

x |

x |

x |

x |

|

n-1 |

0 |

0 |

0 |

x |

0 |

1 |

|

n |

1 |

0 |

0 |

x |

0 |

0 |

Veja que uma condição importante para o funcionamento deste circuito é que ele comece a funcionar com o valor correto colocado no primeiro estágio ou no estágio que se deseja.

Pode-se garantir que o circuito comece a funcionar sempre com a "programação" correta com a utilização de um circuito apropriado. Quando o contador tem este recurso dizemos que se trata de um circuito "self start".

Outro problema que pode ocorrer com um contador em anel é que ele adquira uma sequência de estados nas saídas dos estágios do qual ele não consiga mais sair, como mostrado na figura 102.

Isso exige que o circuito tenha recursos para corrigir este problema, o que pode ser conseguido com o que se denomina de "auto correção" ou "self correcting".

O circuito mostrado na figura 103 possui os recursos indicados para uma sequência de 10 estágios. Em outras palavras trata-se de um contador em anel de 10 estágios com o recurso de self-correcting e self-start.

Neste circuito, QD é o bit mais significativo ou MSB.

Utilizando outros circuitos integrados, inclusive com tecnologia TTL, podemos implementar contadores de mais estágios

O contador Johnson

Neste tipo de contador a saída complementar do último estágio é que realimenta a entrada do circuito. Na figura 26 temos um exemplo de contador Johnson de 4 estágios usando flip-flops do tipo J-K.

Quando a alimentação do circuito é estabelecida todos os flip-flops são ressetados. Isso é conseguido pela rede formada pelo resistor de 1 k ohms e pelo capacitor de 1 nF.

O que ocorre é que no instante em que a tensão é estabelecida no circuito o capacitor se encontra descarregado. Neste momento, com a forte corrente de carga fluindo pelo capacitor a tensão nas suas armaduras é praticamente zero sendo este nível estabelecido nas entradas CLR dos flip-flops o que os resseta.

Uma fração de segundo depois, com a carga do capacitor sendo atingida, a corrente no circuito deixa de fluir e o nível lógico nas entradas CLR passa a alto, liberando seu funcionamento.

Na figura 105 temos as formas de onda nas saídas deste circuito.

Veja que a frequência do sinal de clock é dividida por 8 nesse circuito. Na verdade, a frequência será dividida por um número que será o dobro do número de estágios do circuito. Por exemplo, um contador de 5 estágios divide a frequência de entrada por 10.

Um problema que pode ocorrer com este tipo de circuito é a entrada num estado que não seja permitido e do qual ele no possa sair. Se isso ocorrer o circuito fica preso numa sequência incorreta de valores digitais apresentados na saída.

Uma maneira de se contornar isso é mostrada na figura 106 em que temos um contador de 4 estágios usando os flip-flops disponíveis nos circuitos integrados CMOS do tipo 4013 e além disso uma porta NOR 4001.

Neste circuito, as entradas CLR dos flip-flops intermediários são usadas para se ressetar o circuito quando um estado proibido que seja, por exemplo, os níveis 1 nas saídas, ao mesmo tempo, do primeiro e último estágio ocorram.

Na figura 107 temos outro circuito de contador Johnson com módulo 3.

As formas de onda são dadas na figura 30.

Este circuito se caracteriza pelo fato de permitir a contagem em módulos de valores ímpares. Observe que os circuitos podem ser sempre modificados para se obter isso o que pode ser importante nos projetos práticos.

Índice

Curso de Eletrônica Digital – Analógica e Digital – Sistemas de Numeração (CUR5001)

Curso de Eletrônica Digital – A Álgebra de Boole (CUR5002)

Curso de Eletrônica Digital – Famílias de Circuitos Lógicos Digitais (CUR5003)

Curso de Eletrônica - Eletrônica Digital – A Família de Circuitos Integrados CMOS (CUR5004)

Curso de Eletrônica Digital – Combinando Funções Lógicas - (Lógica Combinacional) (CUR5005)

Curso de Eletrônica - Eletrônica Digital - Os Elementos Biestáveis (CUR5006)

Curso de Eletrônica - Eletrônica Digital - Flip-Flops e Funções Integradas em CIs (CUR5007)

Curso de Eletrônica - Eletrônica Digital - Os Multivibradores Astáveis e Monoestáveis (CUR5008)

Curso de Eletrônica - Eletrônica Digital - Os Contadores Digitais (CUR5009)

Curso de Eletrônica - Eletrônica Digital - Memórias, ADCs e DACs (CUR5013)