A Intersil descreve um circuito que permite obter um clock em tempo real (RTC), usando como referência a frequência de 60 Hz da rede de energia. Neste artigo procuramos passar de uma forma adaptada o projeto descrito para o leitor!

Nota: O artigo é de 2008.

A maioria dos circuitos que necessitam de um clock preciso, faz uso de osciladores controlados cristal. Estes componentes oferecem boas precisão, se bem que sofram pequenas alterações de suas características em função de temperatura. Essas pequenas alterações podem, entretanto, não ser tão pequenas em uma aplicação muito crítica. Um deslocamento de 100 ppm em um clock que comande um relógio, por exemplo, pode resultar em um desvio de 1 minuto por semana. Em um caso como este, um recurso para se manter a temperatura do cristal constante é muito importante para se garantir a precisão.

Uma forma interessante de se obter uma referência de tempo precisa, quando possível, é com o uso da frequência da rede de energia. Por lei, a frequência deve ser mantida dentro de valores precisos, uma vez que existem muitos equipamentos que se utilizam da mesma como referência. Assim, neste artigo, descrevemos um circuito simples que faz uso de componentes da Intersil, para se obter um sinal de 4 Hz de grande precisão.

O circuito

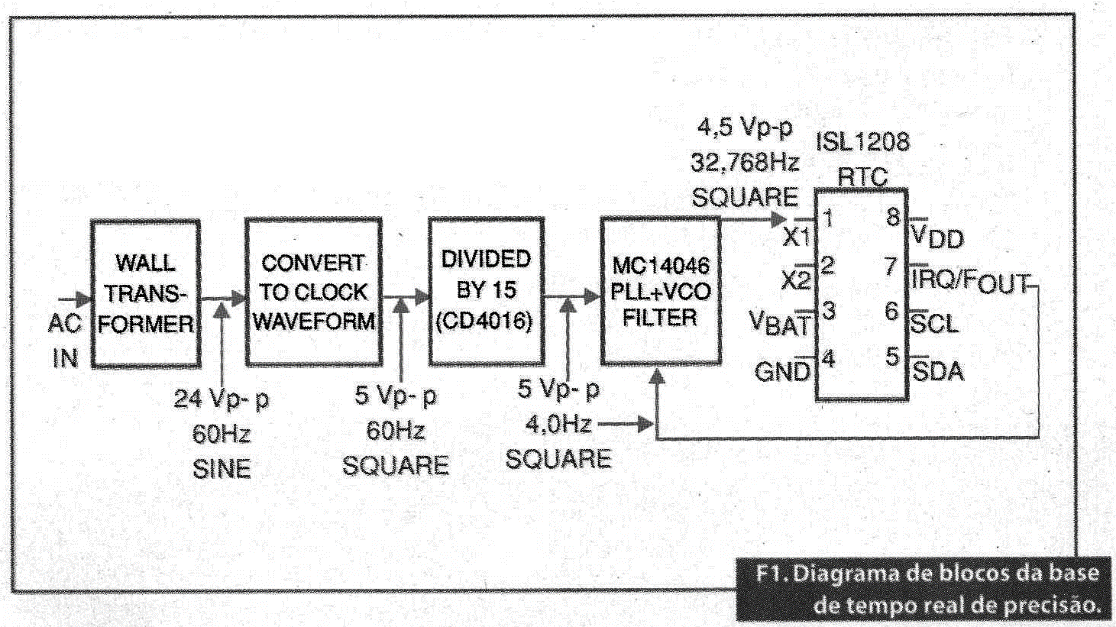

Para se obter uma referência precisa, o que se faz é a divisão sucessiva do sinal que então é aplicado a um dispositivo RTC como o ISL1208 da Intersil, conforme diagrama de blocos mostrado na figura 1.

O que ocorre é que na maioria dos dispositivos RTC a entrada é feita através de um oscilador a cristal de 32,768 kHz, sendo então feita a divisão interna deste valor para se obter um sinal de 1 Hz. O RTC não aceita um sinal de clock de 60 Hz, de modo que deve ser utilizado um PLL para se obter a frequência correta, ainda mais porque 60 Hz não é um submúltiplo de 32,768 kHz.

Assim, conforme mostra o diagrama de blocos, o que se faz é usar uma referência de entrada de 60 Hz, dividindo este valor para se obter 4,0 Hz, o qual é aplicado a um PLL que fornece de saída o clock de 32,768 kHz. O RTC usa então esse valor como clock interno e faz a divisão para se obter novamente 4,0 Hz de modo que esse valor funcione como detector de erro para o PLL.

No primeiro bloco do circuito temos um transformador que fornece uma tensão senoidal de 24 V pico a pico com uma frequência de 60 Hz. Na verdade, o circuito precisa de pelo menos 4 Vpp para funcionar, o que quer dizer que transformadores de 9 V a 30 V podem ser utilizados, conforme indica a Intersil.

A entrada do circuito é diferencial, sendo usados resistores de 1,2 k ohms para limitar a corrente. Acorrente é retificada em meia onda de modo a se poder gerar o sinal para o bloco seguinte. Este bloco tem por finalidade converter o sinal senoidal num sinal quadrado de 5 Vpp com 60 Hz de frequência. O sinal será aplicado a um divisor por 15 formado em torno de um circuito integrado CMOS 4016, obtendo-se assim um sinal de 4 Hz com ciclo ativo de 50%.

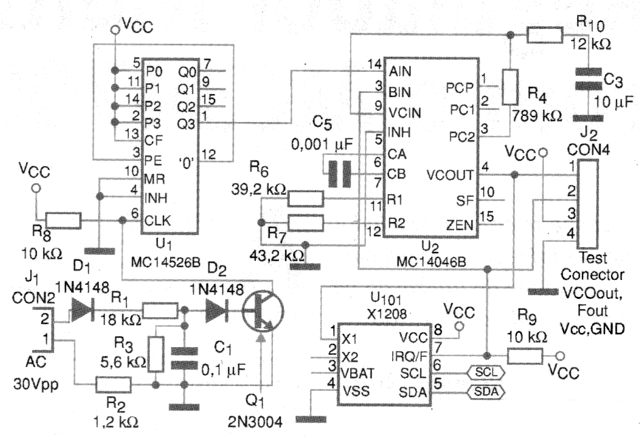

Ele ainda será empregado como referência para o PLL. No bloco seguinte temos um PLL mais um filtro VCO baseado em um circuito integrado 4046. O sinal é então utilizado para que em conjunto com o PLL seja gerado o sinal final de 32,768 kHz com estabilidade. Na figura 2 temos o diagrama completo do clock.

Detalhes do cálculo dos componentes utilizados no PLL podem ser obtidos no application note AN1342.0, o qual está disponível no site da Intersil (www.intersil.com) em formato PDF para download.