O circuito apresentado faz a divisão de frequência de sinais TTL por valores programados entre 1 e 256. Este circuito pode ser usado como base para sintetizadores de frequências, relógios, cronômetros e outros dispositivos que necessitem da função especificada. Os integrados usados são comuns e para programação existem diversas opções.

A base deste divisor de frequência é o integrado 74161 que consiste num contador binário (divisor por 16) que possui Clear e pode ser programado externamente através de 4 entradas.

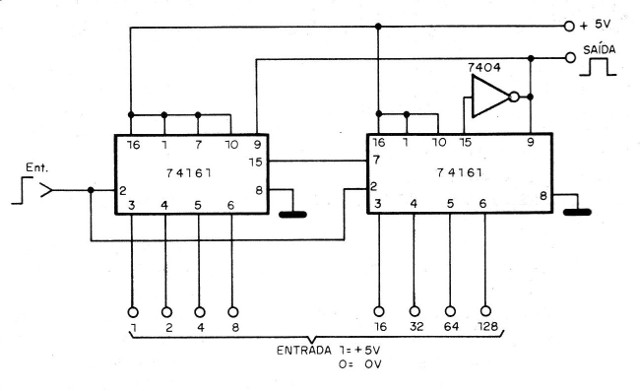

Com a utilização de duas unidades 74161 podemos ampliar a capacidade de divisão de frequência de 24 (16) para 28 (256) e com isso chegar à finalidade do projeto.

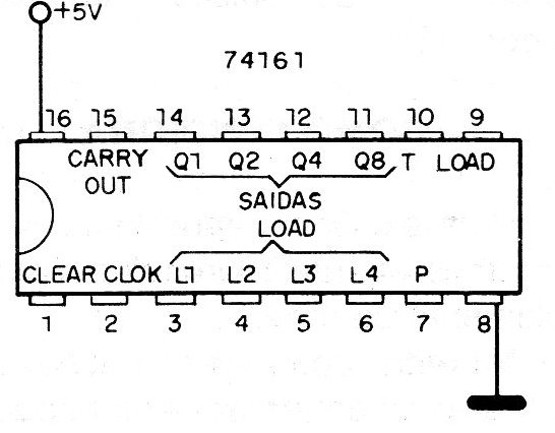

Na figura 1 temos a pinagem do integrado 74161 que é a base do projeto.

Para a operação normal, as entradas Clear, Load, P e T são levadas ao nível HI.

Nestas condições, o contador avança uma unidade a cada transição do clock do nível baixo para o nível alto (fonte positiva do sinal).

A frequência máxima de operação do integrado e, portanto, de entrada é de 25 MHz.

As saídas de Q1 a Q8 são saídas binárias enquanto que as entradas Load de L1 a L8 são para a programação da contagem.

Para zerar o contador, basta ligar a entrada Clear momentaneamente à terra.

Para programar o divisor basta aplicar os sinais correspondentes aos níveis nas entradas correspondentes.

Assim, para programar a divisão por 98 fazemos as entradas 1,4,8,16,32,64,128 nos níveis respectivos: 01000110.

No segundo integrado temos um circuito de “vai um“ elaborado com um inversor dos 6 existentes num 7404.

O sinal digital obtido tem forma de onda retangular. A corrente em cada integrado é de 34 mA.

Na figura 2 temos o circuito completo do divisor.

Evidentemente, como se trata de circuito a ser incorporado em projetos mais complexos, não será necessário dar a placa de circuito impresso que deve ser projetada de acordo com cada caso.