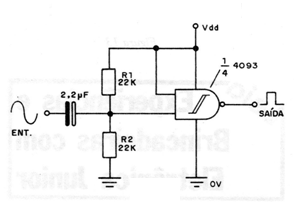

O circuito apresentado na figura converte um sinal senoidal de amplitude conveniente num sinal retangular compatível CMOS. Os resistores R1 e R2, tipicamente de 22 k determinam a impedância de entrada do circuito enquanto que C1 deve ter seu valor escolhido em função da frequência do sinal senoidal de excitação. O capacitor deve apresentar uma baixa reatância na frequência escolhida. Uma aplicação prática deste circuito é como clock para relógios sincronizados a partir da rede de alimentação. Um sinal senoidal de 60 Hz pode ser convertido num sinal retangular de 6oHz para posterior divisão em etapas CMOS.