Os primeiros circuitos lógicos empregavam o diodo como elemento comutador de níveis lógicos. Atualmente esta técnica ainda é usada.

Nota: O artigo é de 1977

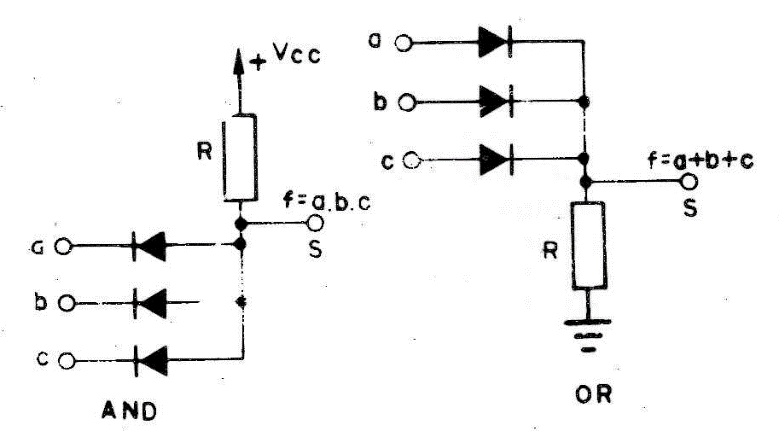

A figura 1 mostra as configurações básicas das portas AND e OR e diodos, ambas com três entradas designadas por a, b e c e uma saída s; esta saída é uma função lógica das entradas.

Para a porta AND, se todas as entradas estiverem em nível lógico alto (H) farão com que os diodos estejam inversamente polarizados, não conduzindo, assim, o potencial da saída, será em nível alto (H). Porém, se apenas uma delas for aterrada (nível lógico baixo — L), o diodo referente a essa entrada passará a conduzir fortemente, curto circuitando os demais levando o potencial de saída a nível baixo (L): quase que a zero volt — em realidade esse potencial é da ordem de alguns décimos de volt, devido à tensão da barreira de potencial da junção do diodo.

Para a porta OR (figura 1) bastará aplicar um potencial alto em, apenas, uma de suas entradas para que o diodo referente passe a conduzir, provocando uma d.d.p. entre os terminais do resistor R; se, no entanto, todas as entradas estiverem em nível lógico baixo, todos os diodos estarão cortados e, portanto, a tensão de saída será interpretada como nível L.

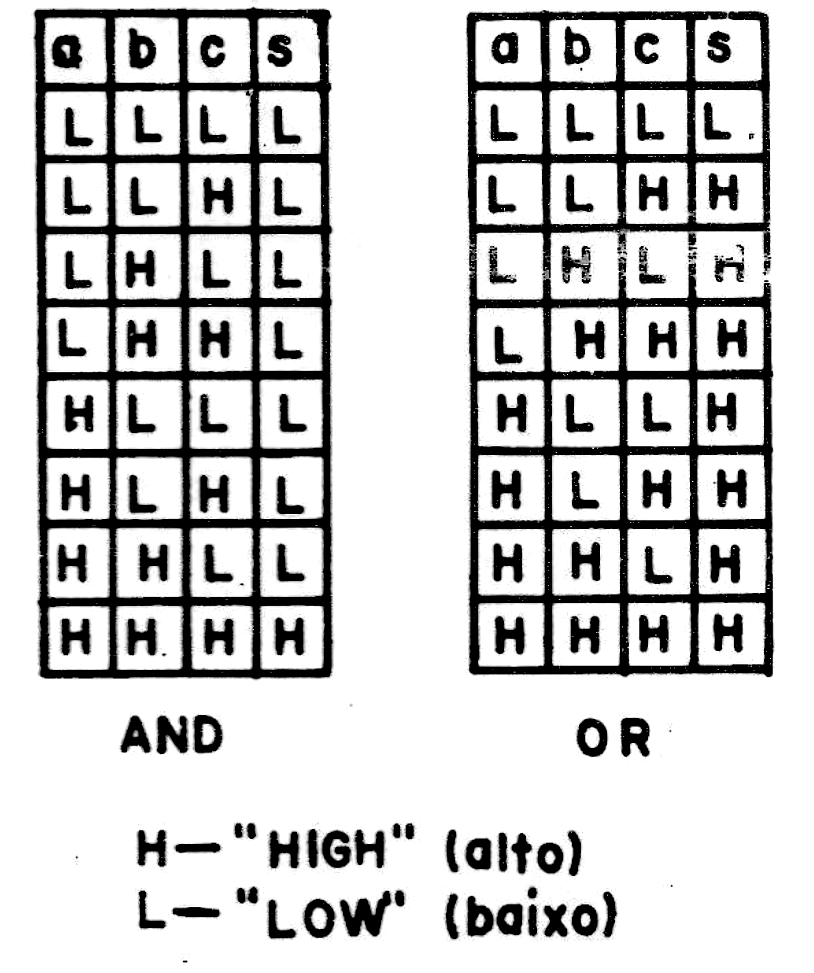

A figura 2 apresenta a tabela lógica para cada uma das portas acima descritas.

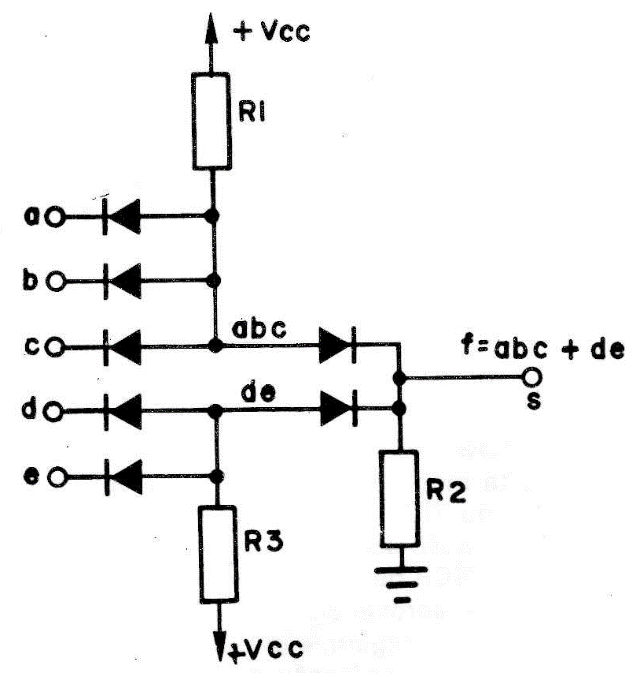

É possível termos circuitos AND seguidos por circuitos OR como o indicador na figura 3, mas não é viável encadear-se indefinidamente os "gates- AND e OR sem amplificação: os diodos juntamente com os resistores apresentam perdas, sendo necessária a interligação a circuitos amplificadores. Nos primórdios, a amplificação era obtida a partir de uma válvula a vácuo funcionando na configuração inversa. Atualmente a função de amplificação e inversão é feita com transistores; vejamos, então, o funcionamento dos transistores.

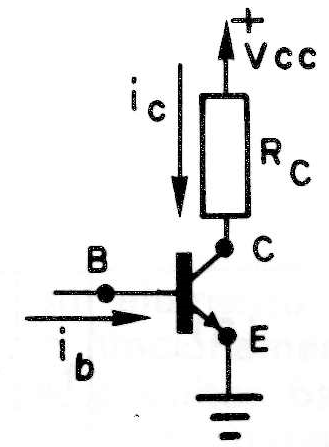

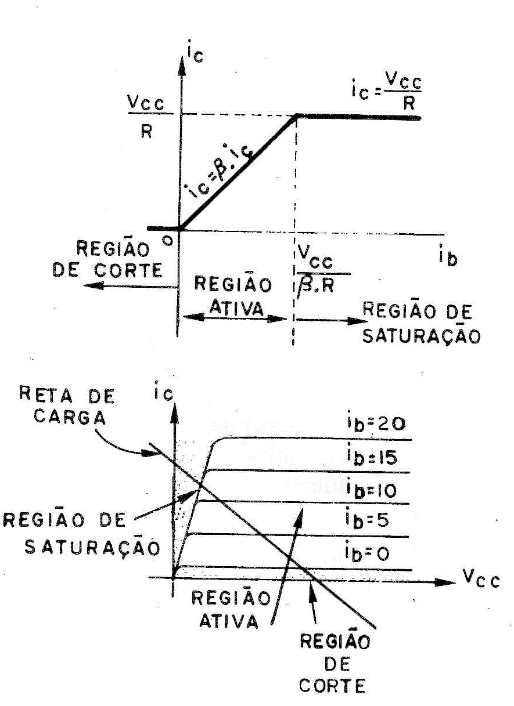

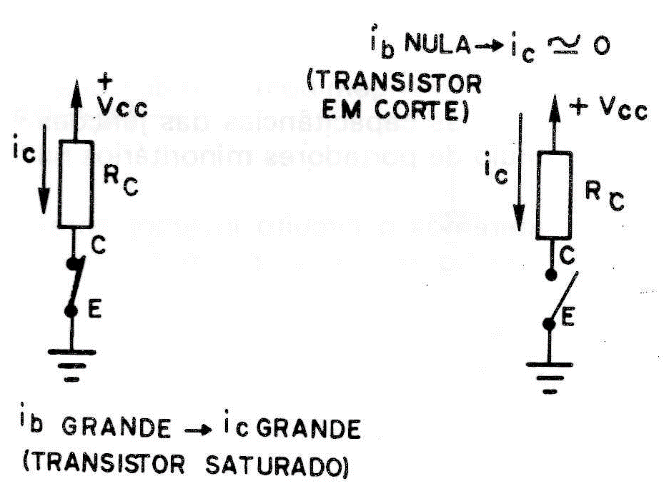

Todo transistor tem seu funcionamento caracterizado por três regiões. Quando a corrente de base (Ib) é nula, o transistor fica na região de corte, isto é, fica aberto — não conduz. À medida que aumentamos a corrente de base Ib, acorrente de coletor Ic vai aumentando proporcionalmente Ic = ßib), caracterizando a região de amplificação ou região ativa; se aumentarmos a corrente de base até chegarmos á igualdade Ic. R = Vcc (figura 4), o transistor estará operando na região de saturação.

Na região de corte o potencial do coletor (Vc) em relação a terra é praticamente Vcc, isto é: Vce ≂ Vcc; na região ativa temos, 0 < Vc

Posto isto, verificamos que o transistor pode operar como um comutador ou chave: quando injetamos uma corrente suficientemente grande na sua base, a "chave" fecha (o coletor é ligado à terra), quando a corrente de base é nula, a "chave" fica aberta. Os circuitos equivalentes a estes dois estados podem ser vistos na figura 6.

Ao operar-se com o transistor como chave, deve-se passar o mais rapidamente possível pela região ativa; se o transistor estiver cortado deve-se saturá-lo imediatamente passando-se o mais rapidamente possível da situação ib = O (cortado) para a situação

ib > Vcc / ß x R (saturado)

Em resumo, podemos dizer que as três regiões de operação são caracterizadas conforme se segue:

corte → ib = 0

ativa → 0 < ib < Vcc / ß x R

saturação → ib > Vcc / ß x R

Para análise das curvas da figura 5 percebe-se que, quando o transistor está saturado, a tensão de coletor não é exatamente zero, nem quando cortado a corrente de coletor é nula. Estes valores dependem do tipo de transistor e do ponto de operação. Normalmente, os transistores de silício, quando saturados, apresentam um VCE em torno de 0,4 volts enquanto os de germânio na mesma condição apresentam um VCE de saturação (VCE sat) em torno de 0,2 volts; no estado de corte estes mesmos transistores apresentam, respectivamente, os seguintes valores típicos (base aterrada):

Ico ≂ 1 nA ≂ 0,25 nA e

Ico ≂ 1 uA ≂ 0,25 uA

A comutação de um transistor da região de saturação para a de corte e vice-versa não é instantânea como já dissemos: somente, algum tempo após a aplicação do estímulo ao transistor, o mesmo responde; este tempo de demora (tempo de transição) é de vital importância para os sistemas digitais, principalmente os de computação. A origem do tempo de transição deve--se às capacitâncias das junções e o acúmulo de portadores minoritários na base.

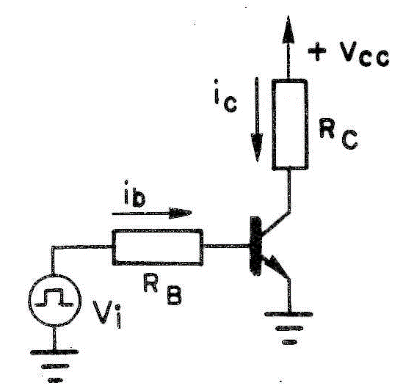

Consideremos o circuito inversor apresentado na figura 7 e apliquemos á base do transistor a forma de onda vista na figura 8—A; o transistor responderá a este estímulo conforme é visto na figura 8 B. Observar os tempos de atraso de "subida" ("turn-on time") e de "descida" ("turn-off time") — estes tempos de atraso são conhecidos por tempo de retardo de acionamento e tempo de retardo de desativamento respectivamente.

O "turn-on time" é formado por dois tempos:

— td — "delay time" (tempo de atraso) e

— tr — "rise time" (tempo de subida) em que: td + tr -= tON.

O "delay time" é contado desde a subida da entrada até que ic atinja 10% da corrente de saturação de coletor (0,1 ICsat); o "rise time" é contado a partir do instante em que ic(90% da = 0,9 ICsat corrente de saturação de coletor).

O "delay' time" é contado desde a subida da entrada até que IC atinja 10% da corrente de saturação de coletor (0,1. ICsat); o "rise time" é contado a partir do instante em que IC = 0,1 ICsat até que IC = 0,9 ICsat (90% da corrente de saturação de coletor).

O "turn-off time" também é composto por dois tempos, a saber

- ts - "storage time" (tempo armazenamento) e

- rf - ""fall-time" (tempo de descida) em que: ts + tf = tOFF.

O "storage time" é contado a partir da descida do sinal até que Ic = 0,9 Icsat; e/ "fall time" é contado desde o instante em que ic = 0,9 Icsat até o instante em que se verifica

Ic = 01 . ICsat.

A maioria das publicações técnicas emprega o termo "delay" (atraso) indistintamente para os tempos "turn on" e "turn off". A ordem de grandeza para a maioria de transistores é de alguns nanossegundos (1 ns = 10-9 s.).

Com este estudo constatamos que a velocidade de comutação dos circuitos lógicos a transistores está intimamente ligada à característica da velocidade de resposta dos mesmos. Vários são os métodos empregados para minimizar os tempos de atraso; a sua análise foge ao escopo deste trabalho.

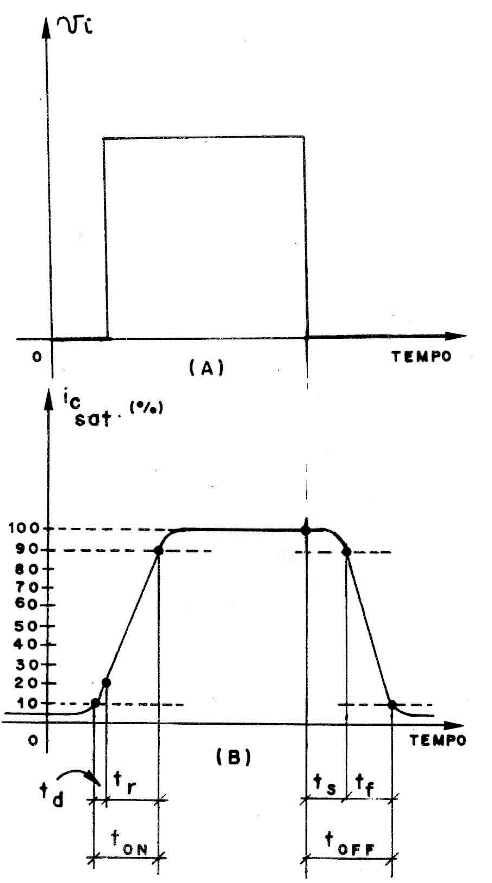

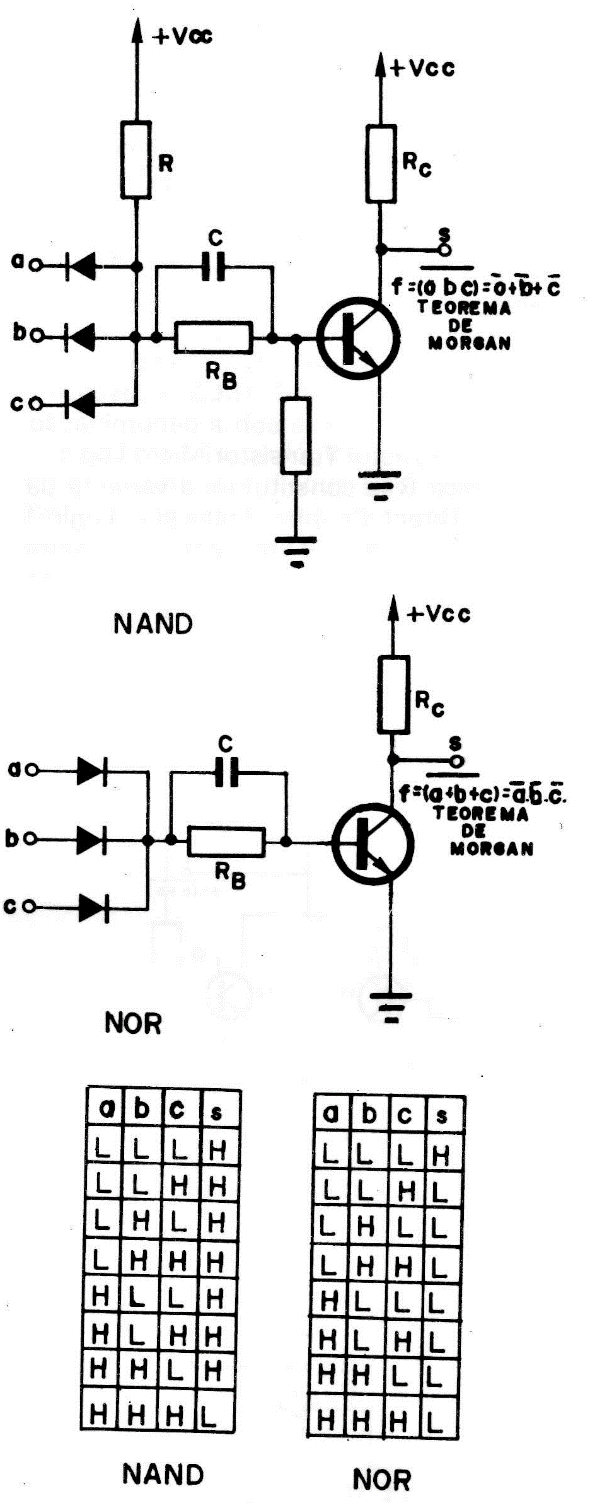

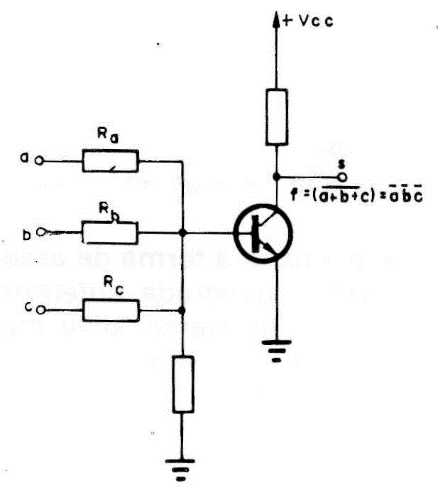

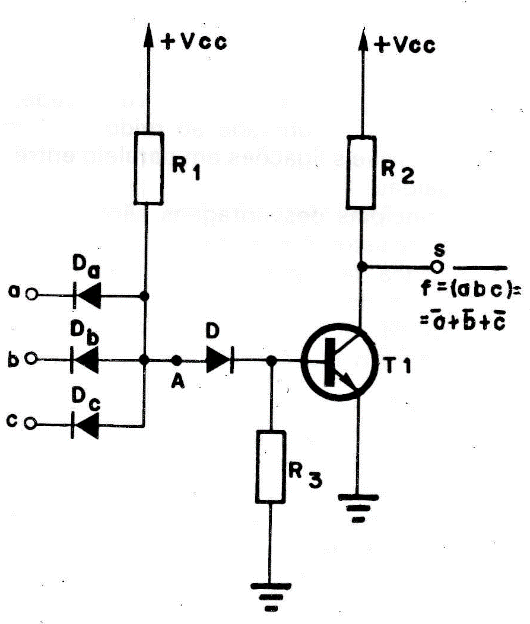

A figura 9 mostra a forma de associar a lógica a diodos, mostrada anteriormente (figura 1), a um elemento ativo inversor. Para estudar o funcionamento e a tabela verdade destes circuitos basta raciocinar da seguinte maneira: quando a tensão na entrada da base do transistor é alta (H), existe uma grande corrente na referida base que satura o transistor, isto faz com que sua saída (em coletor)caia para zero ou próximo de zero (nível L); se a tensão de entrada for zero ou próxima (nível L), a corrente de base será praticamente nula, levando o transistor ao corte e, portanto, a tensão de coletor será, em primeira aproximação Vcc, isto é, alta (nível H).

Os Cl (circuitos integrados) lógicos são classificados em famílias, cada qual apresenta características bem definidas e áreas de aplicação relativamente específicas. Em verdade, entende-se por família, um conjunto de operadores fabricados a partir de um mesmo esquema básico, resultando em consequência propriedades comuns e notadamente compatibilidade. O projetista não mais se preocupa com o circuito propriamente dito e sim, somente com a interligação dos blocos operadores. A escolha de uma ou outra família só poderá ser feita pelo projetista se o mesmo conhecer as vantagens e desvantagens de cada uma dessas famílias.

O estudo que se segue está limitado a operadores lógicos binários eletrônicos de maior utilização.

Família RTL ("Resistor Transistor Logic") Esta foi a primeira família que surgiu no mercado sob a forma de CI, sendo uma transposição em versão integrada de montagens equivalentes com componentes discretos. Cabe à FAIRCHILD o desenvolvimento desta família sob a denominação de RTL ("Resistor Transistor Micro Logic").

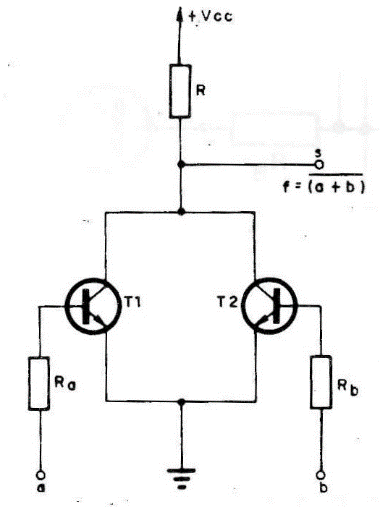

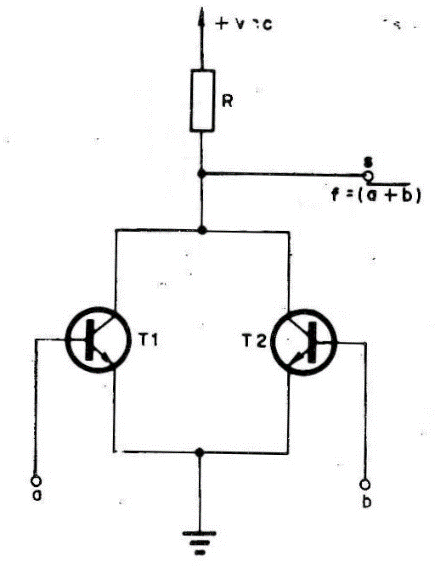

A lógica RTL constitui uma variante da DCTL ("Direct Coupled Transistor Logic") cujo operador NOR é apresentado na figura 10. Observar, por simples comparação entre as figuras 10 e 11 que a RTL nada mais é do que a DCTL quando a mesma se anexa um resistor a cada base dos transistores T1 e T2.

Quando as entradas estão a um potencial próximo de terra, os transistores T1 e T2 estão cortados e a saída s estará num potencial próximo a Vcc — nível lógico H. Se for aplicada uma tensão positiva em uma ou em ambas entradas a e b, a saída s estará num potencial próximo a zero pois um ou ambos os transistores ficará saturado (VCE 0). Este tipo de lógica toma o nome de lógica saturada pois para os transistores se conhecem dois estados: um bloqueado e outro saturado.

A figura 12 mostra outro circuito possível para o operador NOR da família RTL; seu funcionamento é semelhante ao anteriormente descrito.

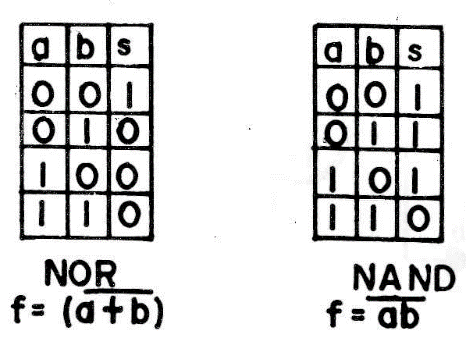

A potência dissipada por porta e o tempo de propagação dependem dos valores atribuídos aos resistores de base. Quando eles apresentam valores baixos, como acontece na RT µL, o tempo de propagação, isto é, o "tON " ou "tOFF" é da ordem de 10 µs e a potência dissipada com as duas entradas em estado alto é de 20mW e, em estado baixo (transistores cortados) a potência dissipada é de 5mW; estes dois valores fornecem a potência média de dissipação de 12 a 13mW. Com valores altos para os resistores, como sucede na lógica MwµL ("Mili Watt Micro Logic") da FAIRCHILD, o tempo de propagação passa à 40 µs e a potência média dissipada é da ordem de 2mW. O raciocínio desenvolvido até agora baseou-se em termos de lógica positiva, isto é, uma lógica para a qual o nível lógico "1" é definido pela tensão (positiva) mais alta (normalmente, em torno de Vcc) e o nível lógico "O" é atribuído à terra ou próximo. Mas se empregarmos uma lógica negativa com a mesma porta fundamental NOR, a mesma se comportará como uma porta NAND conforme se constata com as tabelas verdade da figura 13. Isto prova, simplesmente, que a mesma porta RTL executa as operações ou funções lógicas NOR em lógica positiva e NAND em lógica negativa.

Em tempo: a lógica negativa se caracteriza por atribuir ao estado lógico "1" o menor valor da tensão e o "O" está associado ao potencial Vcc. A principal vantagem desta família é a baixa potência dissipada, sendo ideal para situações em que o consumo é um fator preponderante, além disso o custo destes Cl é baixo, em virtude do número reduzido de componentes que emprega; é possível ainda, empregar a lógica desta família com componentes discretos.

Uma desvantagem desta família é a sua lentidão pois o resistor em série com a base (figuras 11 e 12) e a capacitância da junção base-emissor forma uma rede RC que aumenta os tempos de "turn-on" e "turn-off". Poderíamos pensar em acrescentar um capacitor em paralelo com o resistor de base conforme é mostrado na figura 9, porém, esta solução é inaplicável para os Cl devido ao grande volume exigido pelo capacitor; tratando-se de componentes discretos a solução se justifica e teremos então, a família RCTL ("Resistor Capacitar Coupled Logic") que é outra forma da família RTL.

O "FAN—OUT" (o "fan-out" é a quantidade máxima de entradas de blocos de uma mesma família que podem ser ligadas à sua saída; o "FAN—OUT" mede, grosseiramente a potência de saída do circuito) desta família se encontra em torno de 4, que é baixo.

A RCTL foi comercializada no início da década 60-70 pela TEXAS, diferindo da RTL da FAIRCHILD apenas, como vimos, pela introdução de um pequeno capacitor de aceleração em paralelo com cada resistor de base; permitindo realizar a função NOR em lógica positiva e a função NAND em lógica negativa.

Família DTL ("Diode Transistor Logic").

A família DTL ou lógica a diodo e transistor recorre aos diodos para realizar as funções lógicas e aos transistores para amplificar e inverter os sinais. A figura 14 mostra a estrutura básica da porta fundamental (NAND) desta família: NAND em lógica positiva e NOR em lógica negativa. Observar que todas as entradas devem estar em nível H simultaneamente para que a saída esteja em nível baixo (L)

O diodo D serve para aumentar a imunidade do gate ao ruído; não existindo este diodo, ao aplicar-se um sinal L numa das entradas, a saída do gate AND (ponto A da figura 14) apresentaria um nível lógico, também baixo, na ordem de 0,5 volt como um, mínimo, dependendo do diodo D1 e do

sinal de entrada, este sinal colocaria o transistor no limite entre o corte e a saturação e qualquer ruído, isto é, qualquer perturbação para cima deste sinal de entrada, poderá levar o transistor à região ativa que, dependendo do ganho do mesmo, poderá saturá-lo (ou quase saturá-lo), mudando sua saída s. Com a presença do diodo D estamos assegurando que o potencial da base está, aproximadamente, 0,5 volt abaixo do potencial do ponto A impedindo que o transistor conduza se o sinal no ponto A (saída do gate AND) for de baixa amplitude — 1,0 volt aproximadamente.

Muitos dos Cl comerciais empregam não só um diodo, mas sim dois com a finalidade de aumentar ainda mais a imunidade do circuito a ruídos

A finalidade do resistor R3 é a de diminuir o tempo de "turn-off".

Esta família é do tipo de lógica saturada, apresentando as seguintes vantagens:

— nível lógico elevado;

— FAN—OUT moderadamente grande;

— FAN—IN limitado pela fuga dos diodos. (Entende-se por "FAN—IN" como o número de entradas de um bloco lógico); bom compromisso entre velocidade, consumo e imunidade ao ruído; — são possíveis ligações em paralelo entre as saídas As principais desvantagens são:

— exige resistores precisos;

— diferença de impedância de saída para cada um dos níveis lógicos, sendo, portanto, diferentes os tempos de propagação para o nível alto e baixo.

Com a finalidade de aumentar ainda a imunidade a ruídos e estabilizar o circuito, costuma-se, em vez de aterrar o resistor R3 (figura 14) ligá-lo a uma fonte negativa de tensão em torno de 2,0 volts. Isto traz um novo inconveniente: é necessário empregar duas fontes para alimentar o circuito.

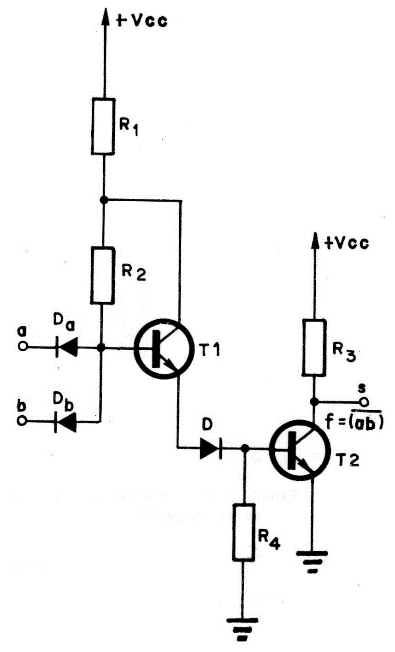

Para evitar os inconvenientes próprios da DTL fundamental, recorre-se à DTL modificada cujo circuito básico de seu operador fundamental (porta NAND) é mostrado na figura 15. A diferença fundamental para o circuito, diremos, original é a presença de transistor T1 que opera na região linear, amplificando o sinal aplicado em sua base. A presença do transistor T1 aumenta a imunidade do ruído do circuito sem a necessidade de uma tensão negativa de alimentação, além disso aumenta o FAN--OUT para 8, melhora a relação entre a potência dissipada e frequência de operação.

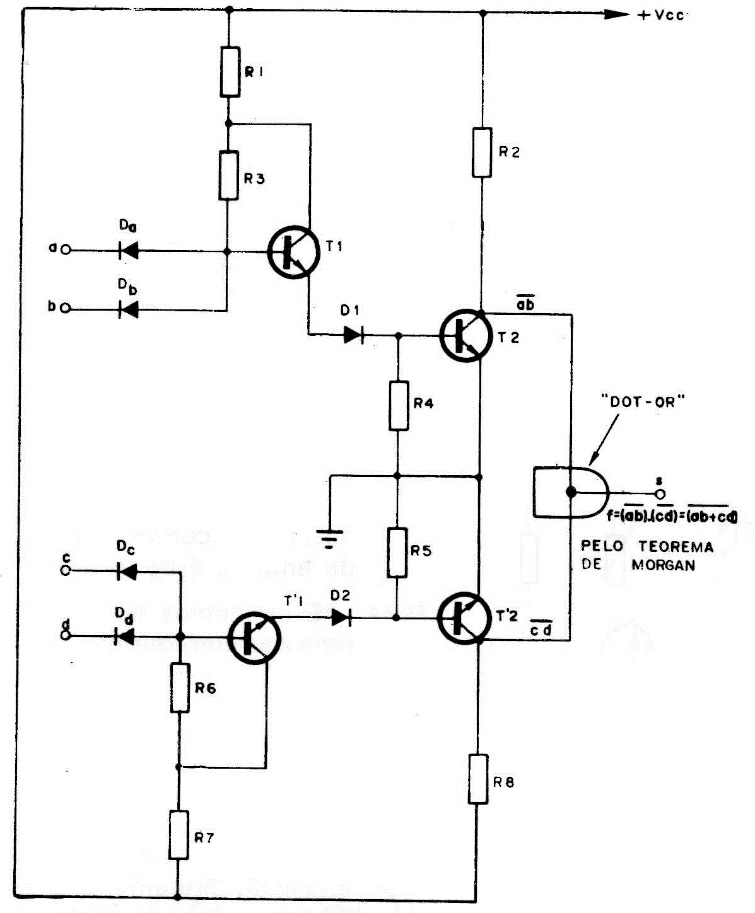

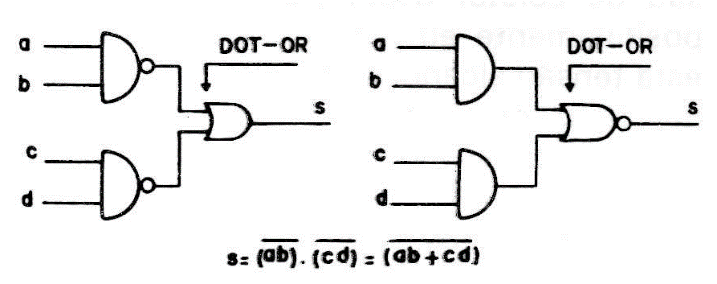

A estrutura desta lógica permite a interligação das saídas de diversas portas a fim de realizar o que se conhece por 'função gratuita" ou cablado (em inglês: "DOT--OR" ou "Wired-OR", ou, ainda, "Implied--AND"); assim, se tomarmos dois NAND e ligarmos suas saídas em curto, tal como é mostrado na figura 16, teremos, com esse ponto de ligação, realizado uma função AND, pois esse ponto só estará no nível lógico H (lógica positiva) se os dois NAND tiverem suas saídas em nível H; um dos NAND tendo sua saída L é suficiente para que o "ponto" caia a L pois seu transistor de saída saturado drena a corrente dos dois resistores, aterrando o referido ponto. O circuito equivalente é mostrado na figura 17 em duas configurações; observar que tanto se pode realizar, neste ponto, a função AND como a OR em virtude do teorema de Morgan.

A imunidade ao ruído da porta DTL encontra-se em torno de 1,0 volt; para aumentar esta imunidade, como já vimos, basta introduzir ao circuito básico (figura 14) mais diodos, conhecidos por diodos de deslocamento de tensão em virtude da função que realizam, em série, conectados à base do transistor T1; cada um deles individualmente fará um deslocamento de 0,2 ou 0,6 volt dependendo se o mesmo é de germânio ou silício respectivamente; o entanto, com um único diodo podemos resolver a questão, é claro, se este diodo for Zener. Realmente não se emprega um diodo Zener propriamente dito e sim uma junção de transistor inversamente polarizada funcionando em avalanche que, aliás, é o que caracteriza o diodo Zener.

A "técnica" acima é empregada pela AEG— Telefunken nas famílias DTL-Z e DTL — FZ sendo muito semelhantes entre si; a imunidade ao ruído em tensão é da ordem de 5,0 volts para uma alimentação de 13,5 volts.

Mesmo com todos os artifícios descritos, a família DTL "peca" por apresentar diferença de impedância na saída quando em nível H e em nível L.

Família TTL ("Transistor Transistor Logic").

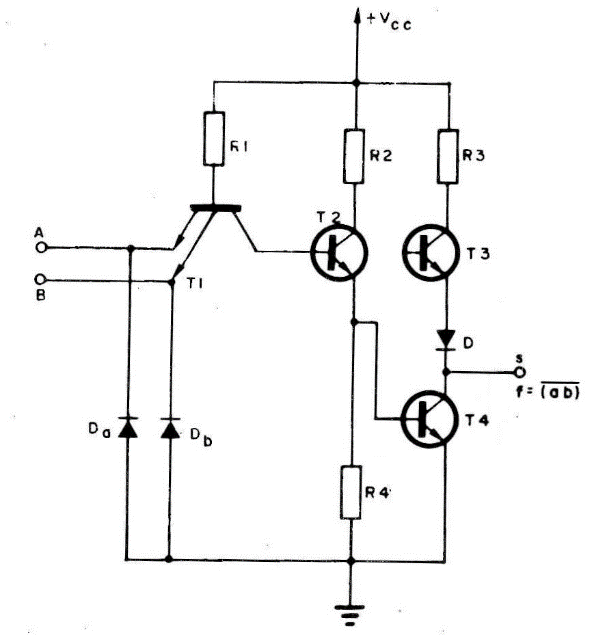

A família TTL ou lógica transistor a transistor é um adianto sobre a família anterior sendo atualmente a família à lógica saturada que encontra mais aceitação no mercado internacional. Os circuitos lógicos desta família são apenas realizáveis sob a forma integrada em virtude do transistor multiemissor de entrada em substituição à rede de diodos da família DTL sendo esta, a diferença fundamental entre estas duas famílias.

A integração monolítica é totalmente explorada na entrada, o transistor multiemissor permite ocupar menor espaço na pastilha do que os diodos além de diminuir substancialmente as capacitâncias parasitas resultando, em consequência um bom aumento na velocidade de operação —figura 18.

Com a finalidade de aumentar o FAN--OUT, as portas TTL são providas de um estágio de saída de potência tipo "push - pull" formado pelos transistores T3 e T4 montados em "totem pole" (figura 18). Os diodos de deslocamento de tensão da família anterior são aqui "substituídos" pelas junções base-emissor e base-coletor do transistor T2.

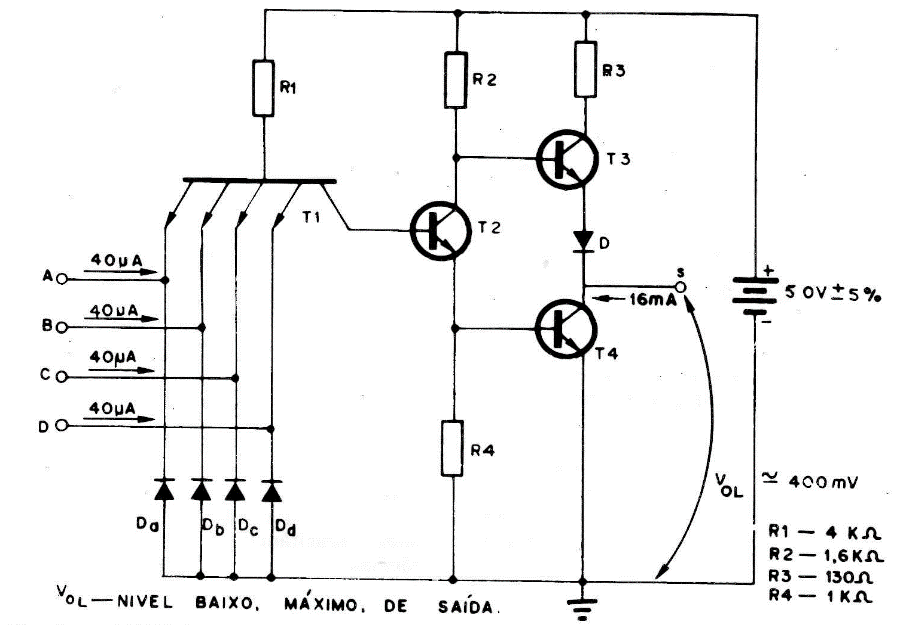

Sendo esta, como dissemos, a família mais popular convém uma análise mais apurada do seu funcionamento e para tal consideremos a figura 19 onde se supõe que todas as entradas estejam nível alto -nível superior a + 2,0 volts com uma corrente de 40 µA em cada entrada. Nestas condições o potencial na base de T1 é da ordem de 2,0 volts em relação a terra, correspondente à soma das quedas das junções: base-coletor de T1, base-emissor de T2 e base-emissor de T4. Os transistores T2 e T4 nestas condições estão saturados e a tensão da saída é a Vcesat de T4 na ordem de 0,3 a 0,4 volts. Como T2 está saturado, a tensão aplicada base à de T3 é, aproximadamente, igual à tensão de seu emissor e, portanto, estará na região de corte. Notar que a tensão aplicada à base de T3, é igual à queda base-emissor de T4 mais Vce de saturação de T2 enquanto a tensão aplicada no seu emissor é a soma da tensão de saturação de T4 (Vce sat) mais a queda provocada pelo diodo D. O transistor T4 em nível baixo deixa passar uma corrente de 16mA sob uma tensão de aproximadamente 0,2 volts o que é suficiente para fornecer um FAN-OUT igual a dez, pois a corrente excitadora, em nível L, de entrada é de 1,6mA.

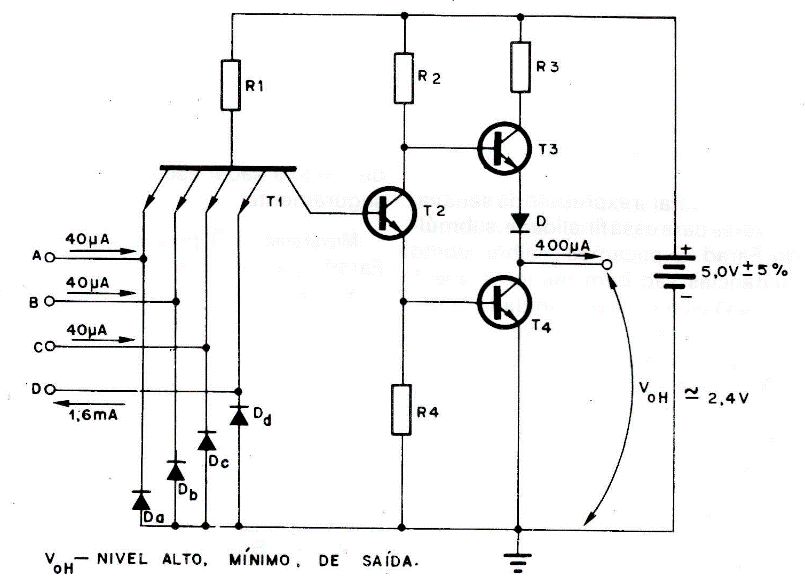

Examinemos agora a situação em que uma das entradas está em nível baixo, com uma VIL (nível baixo máximo de entrada) de 0,8 volts (figura 20). O transistor T1, que funciona em regime de polarização inversa, se encontra desbloqueado. As cargas "estocadas" na junção base-coletor de T1 são multiplicadas pelo ß do transistor, uma forte corrente de coletor se manifesta atacando diretamente a base do transistor T2, que o leva ao corte e, portanto, a tensão de coletor deste transistor aumenta positivamente em direção a Vcc; quando esta tensão alcançar 1,8 volts aproximadamente, o transistor T3 passa a conduzir e como a tensão de emissor de T2 tende a zero, o transistor T4 se bloqueia por sua vez, ficando a saída s em nível alto, sendo no mínimo igual a 2,4 volts - se a tensão de entrada diminuir, a tensão de saída aumentará. Nestas condições verifica-se uma corrente de saída de 400 NA, suficiente para excitar 10 entradas porque, cada entrada em nível alto consome 40 µA - vide figura 19 - isto equivale dizer que o FAN-OUT é igual a 10.

As principais vantagens, desvantagens e características desta família são:

- mais rápida que a DTL: 13ns em valor médio; 8ns para passar de H para L e 18ns para situação inversa, com uma carga capacitiva de 15pF (para uma carga de 150pF este tempo se eleva para 23ns);

- impedâncias de saída equivalentes para os dois estados, sendo baixas: 10 Ω para o estado L e 70 Ω para o estado H;

- boa imunidade ao ruído: em torno de 1,0 volt; - toda a sua linha é facilmente encontrada no comércio especializado em virtude do seu uso generalizado;

- consumo superior ao da DTL: 10mW quando alimentada com 5,0 volts; - não permite o cablado ou função gratuita;

- necessita de desacoplamento a cada 10 gates além de requerer uma alimentação a baixa impedância;

- risco de oscilações;

- grandes consumos de correntes quando da passagem de um nível para outro, drenando grande corrente da fonte de alimentação, o que gera ruídos muitas vezes indesejáveis.