O nome popularmente dado à linha de retardo integrada de “brigada de baldes" (Bucket Brigade) vem do seu próprio princípio de funcionamento. Veja neste artigo como este circuito funciona. O circuito foi muito usado nos anos 80 e 90 quando ainda não existiam os DSPs e FPGAs.

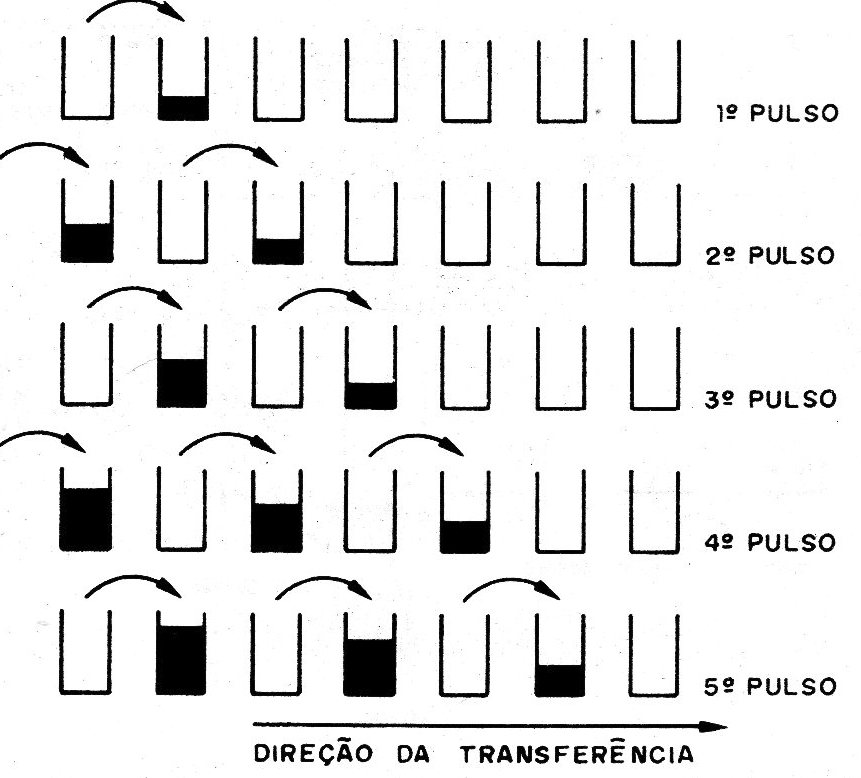

Imaginemos que um sinal aproximadamente senoidal possa ser decomposto em níveis de água numa fileira de baldes, conforme mostra a figura 1.

Cada “ponto” (valor instantâneo) da senoide pode ser associado a um nível de água.

Evidentemente, você perceberá que teremos uma representação tanto mais precisa para a senoide, quanto maior for o número de pontos ou "baldes" usados.

Se quisermos “transmitir" esta senoide adiante, numa enorme fileira de baldes, devemos fazer isso numa sequência de operações de transferência sincronizada, em que jogamos a água de um balde cheio em um vazio adjacente: temos então ciclos de esvaziamento e enchimento de baldes alternadamente, num compasso que "leva” a senoide inteira, conforme sugere a figura 2.

Dependendo do ritmo em que o processo se realiza, e do comprimento da sequência, teremos no final a recuperação da senoide original, mas retardada um certo tempo em relação à entrada.

Quanto mais comprida for a sequência de baldes e mais lento o processo de transferência balde a balde, mais tempo demora para a senoide (ou outro tipo de sinal) atravessar o sistema.

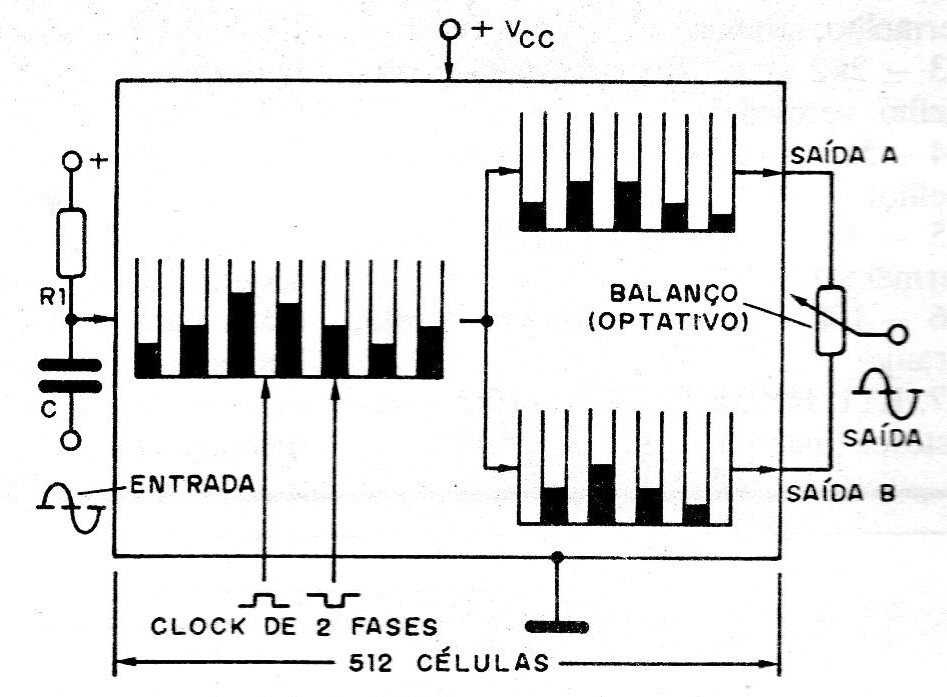

Eletronicamente, os baldes são capacitores que podem armazenar uma carga, cujo valor depende justamente da amplitude do sinal num dado instante.

A esta carga associamos um valor ou ponto da senoide.

Os dispositivos de transferência, ou seja, as “válvulas" que deixam a água passar de um balde para outro, são transistores de efeito de campo (FET).

Na entrada dos dispositivos de transferência aplica-se um sinal “clock", que alternadamente comanda a transferência das cargas de um capacitor para outro, levando assim o sinal adiante.

Pouco antes da saída, o sinal é separado em duas sequências, conforme mostra a figura 3.

A finalidade desta separação é que, havendo duas sequências separadas, no momento em que combinamos os sinais de saída, preenchemos os espaços devido à necessidade de se ter sempre um capacitor “vazio” e outro “cheio" na sequência principal.

As saídas são interligadas e com isso consegue-se a “recuperação" do sinal original aplicado à entrada.

O tempo de retardo para o sinal que se obtém é em função do número de células ou baldes, e também da frequência do clock, mas existem limites práticos bem definidos.

O tempo de retardo para o sinal do TDA1022, em que temos 512 células, é dado pela fórmula:

t = (2 x 512)/f

Onde:

t é o tempo de retardo em segundos

f é a frequência em Hertz

A maior frequência que “passa" pela linha de retardo também depende do tempo de retardo e do número de células.

Teoricamente esta frequência máxima está em torno de 1/3 da frequência do clock.

Assim, para uma frequência de clock em torno de 12 kHz temos um limite da frequência de áudio que passa pela linha em torno de 4 kHz.