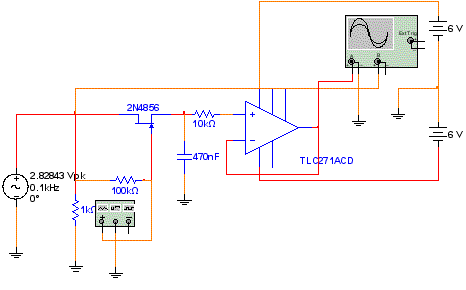

Os circuitos de amostragem e retenção (sample and holding) são muito empregados em conversores analógicos-digitais (A/D). Estes circuitos tomam o valor de uma grandeza e o mantém por um certo tempo registrados na forma de uma carga num capacitor. Este valor pode então ser lido por um conversor de uma forma fixa, num determinado intervalo de tempo. Na figura 1 temos um circuito em que o gerador de função determina os tempos de amostragem com pulsos de 20% de ciclo ativo em 25 ms de duração. O sinal amostrado tem uma frequência de 100 Hz. Para se obter uma saída de baixa impedância, sem carregar o capacitor de modo que ele mantenha o valor da grandeza no intervalo desejado, utilizamos um amplificador operacional com FET do tipo TLC271. Equivalentes podem ser experimentados. A fonte deve ser simétrica e as tensões podem variar conforme a aplicação.

Figura 1 – Circuito de amostragem e retenção.

Na figura 2 temos as formas de onda obtidas no circuito. O traço inferior é da saída do sistema de amostragem e retenção e o superior do sinal analógico da entrada.

Figura 2 – Sinais no circuito

Simulação e netlist estão disponíveis neste link.