Nos projetos de circuitos digitais, surge em alguns casos a necessidade de se dividir a freqüência de um sinal por um número inteiro. Para essa finalidade, o desenvolvedor pode contar com diversas configurações prontas usando componentes comuns. Neste artigo mostramos uma seleção de circuitos divisores de freqüência TTL que podem ser de grande utilidade para os leitores que trabalham com este tipo de tecnologia digital.

Dividir a freqüência de pulsos retangulares em lógica TTL pode ser importante no desenvolvimento de sistemas de aquisição ou transmissão de dados, instrumentação e em muitas outras aplicações.

Se bem que não seja difícil para o desenvolvedor que domine a técnica digital criar o seu próprio divisor baseado nos conhecimentos teóricos de flip-flops e contadores, contar com as configurações prontas é muito melhor.

Por esse motivo, estamos levando aos leitores uma seleção de circuitos divisores de freqüência TTL usando componentes comuns. Os divisores podem ser de diversos tipos, operando sincronizadamente, no flanco positivo ou negativo do sinal, fornecendo ou não sinais simétricos, tudo dependendo dos componentes usados.

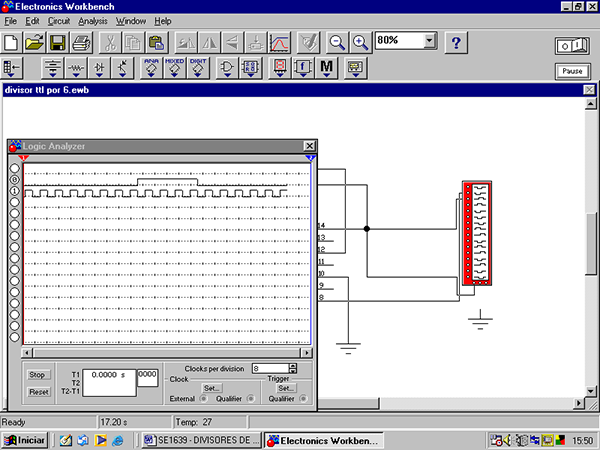

Vários divisores foram simulados no computador para que o leitor possa observar que o sinal de saída nem sempre tem ciclo ativo de 50%.

A velocidade máxima de operação também depende dos componentes usados, podendo ser empregados os CIs das subfamílias mais rápidas, se necessário. Essas velocidades, para os tipos standard variarão entre 18 MHz e 25 MHz, dependendo do componente.

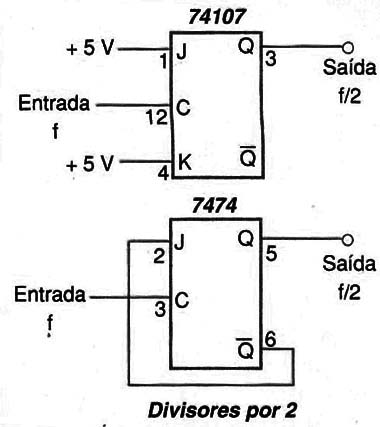

Divisor por 2

O circuito mais simples é o que faz a divisão por 2, havendo duas configurações possíveis baseadas num único flip-flop e mostradas na figura 1.

Nesse circuito, para cada dois pulsos de entrada temos um pulso de saída.

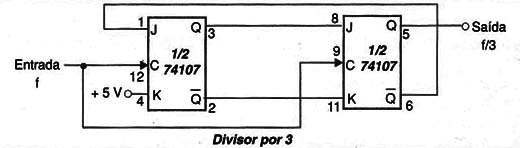

Divisor por 3

O circuito da figura 2 fornece 1 pulso de saída para cada 3 pulsos aplicados à entrada.

São usados os dois flip-flops existentes num circuito integrado 74107. No diagrama não são indicados os pinos de alimentação. O circuito em questão é sincronizado.

Observamos que os sinais de entrada devem ser perfeitamente retangulares para que o circuito funcione satisfatoriamente.

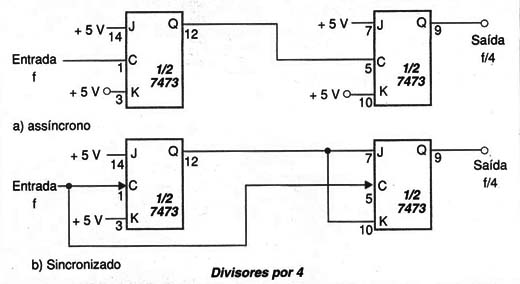

Divisores por 4

Na figura 3 mostramos dois divisores de freqüência por 4, sendo um assíncrono e outro sincronizado.

Neles são usados os dois flip-flops existentes no circuito integrado 7473. Observamos que o ciclo ativo do sinal de saída desses circuitos não é 50%.

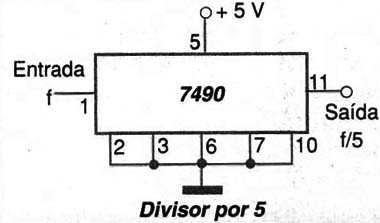

Divisor por 5

Para fazer a divisão por 5 é muito simples, pois podemos contar com o circuito integrado 7490 que já possui em seu interior um bloco lógico com essa finalidade. A conexão desse circuito integrado para fazer a divisão por 5 é mostrada na figura 4.

Observe que não precisamos de nenhum elemento externo adicional nesta configuração. A velocidade máxima de operação é da ordem de uns 18 MHz, para os tipos da série standard.

Tipos das subfamílias H, LS e HC podem operar com velocidades maiores.

No anexo temos a simulação no EWB com as formas de onda obtidas na entrada e saída. O analisador lógico foi empregado com uso de clock externo de 1 Hz e freqüência de prova de 1 Hz com ciclo ativo de 50%.

Observe que o sinal de saída não é quadrado, mas sim retangular com um ciclo ativo menor do que 50%.

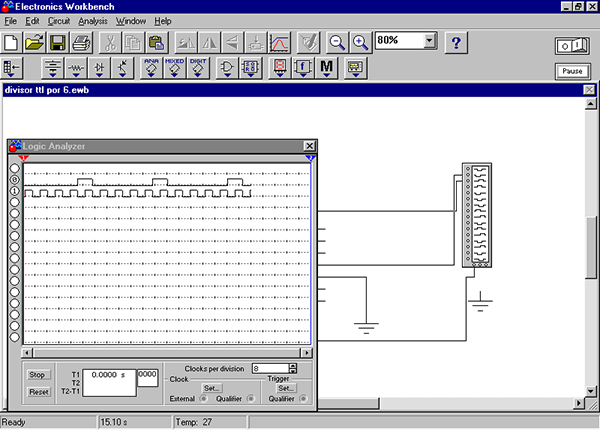

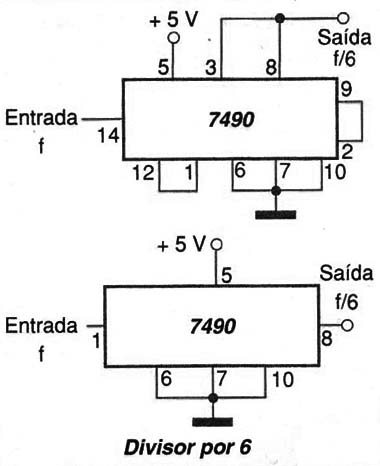

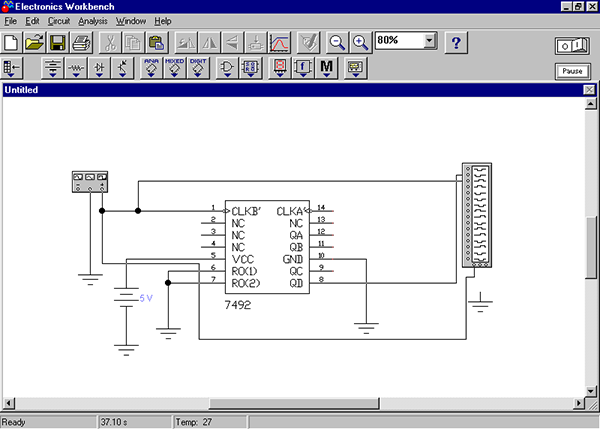

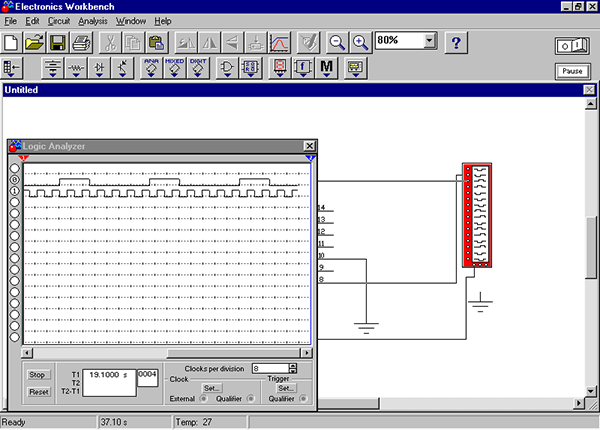

Divisor por 6

Na figura abaixo apresentamos duas configurações de circuitos divisores TTL para a divisão de freqüência por 6.

O primeiro faz uso do tradicional 7490 enquanto que o segundo utiliza o 7492. O 7490 é um contador de década enquanto que o 7492 é um contador divisor por 12. Na divisão por 6 os dois podem ser configurados para operação sem problemas.

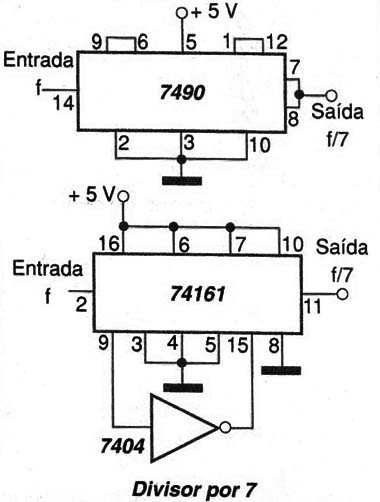

Divisores por 7

A figura abaixo mostra dois circuitos para a divisão de freqüência por 7 usando componentes TTL.

No primeiro caso, um circuito integrado 7490 dá conta da tarefa não necessitando de componentes externos.

No entanto, no segundo caso, como uso de um 74161, que é um contador binário (base 16), é preciso utilizar um inversor externo que pode ser obtido de um 7404.

Obtemos um pulso de saída para cada 7 pulsos de entrada. Observamos que esses pulsos de saída não possuem ciclo ativo de 50%.

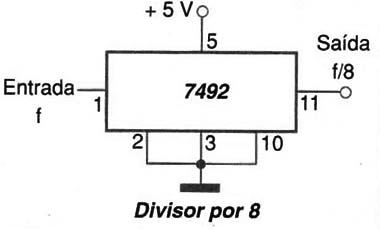

Divisor por 8

A figura abaixo mostra como podemos usar um único circuito integrado 7492 (divisor/contador base 12) na divisão de freqüência de um sinal por 8.

Para cada 8 pulsos de entrada, obtemos um pulso de saída. A velocidade máxima é da ordem de 18 MHz para a série standard e maior para os das subfamílias.

Observamos que, neste caso também, o sinal de saída não é perfeitamente quadrado, ou seja, não tem um ciclo ativo de 50%.

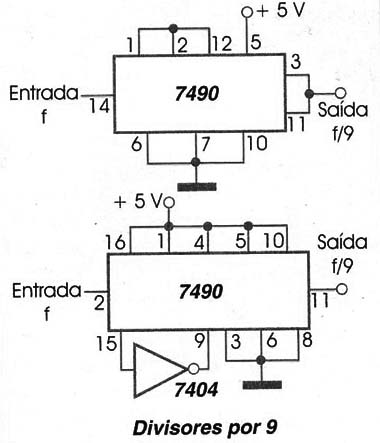

Divisores por 9

A figura 11 mostra 2 configurações para se fazer a divisão por 9 da freqüência de um trem de pulsos TTL.

No primeiro caso usamos um contador de década 7490, cuja velocidade máxima é 18 MHz, sem a necessidade de qualquer componente adicional externo.

No segundo caso, usamos um contador de década 74160 que precisa de um elemento externo, um inversor que pode ser obtido do circuito integrado 7404.

Nos dois circuitos, para cada 9 pulsos de entrada obtemos um pulso de saída.

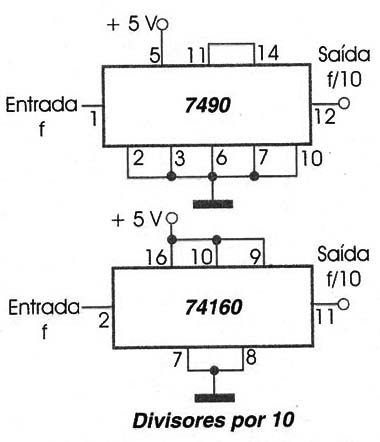

Divisores por 10

Trata-se de uma divisão simples de se obter já que existem circuitos integrados prontos para esta tarefa. Na figura 12 mostramos duas configurações comuns.

São usados os contadores de década 7490 e 74160. O 7490 pode operar numa velocidade máxima de 18 MHz enquanto que a vantagem do 74160 é que ele pode alcançar 25 MHz na versão standard. É claro que componentes das subfamilias podem ser empregados para se obter velocidades ainda maiores.

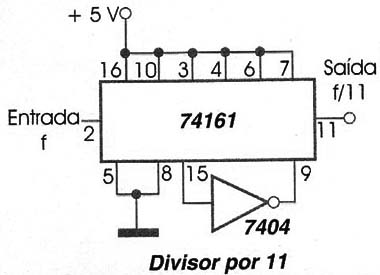

Divisor por 11

Para fazer a divisão de um sinal por 11 precisamos de dois circuitos integrados TTL, conforme mostra a figura 13.

O primeiro é um 74161 que consiste num divisoir binário (base 16) e outro num inversor que tem por finalidade fazer o reset quando se chega na contagem do décimo primeiro pulso.

A velocidade máxima do 74161 é 25 MHz, e o sinal obtido na saída não é perfeitamente quadrado. Seu ciclo ativo é diferente de 50%.

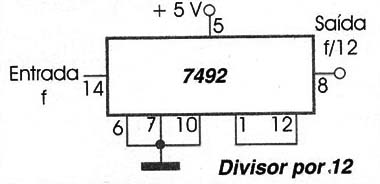

Divisor por 12

Com o circuito mostrado na figura 14 podemos dividir a freqüência de um sinal retangular até 18 MHz por 12.

O 7492 já consiste num divisor/contador até 12 o que facilita a obtenção do circuito. Maiores velocidades podem ser obtidas com componentes das subfamílias.

A simulação no computador mostra que o ciclo ativo do sinal obtido na saída não é 50%. Isso deve ser levado em conta em determinadas aplicações.

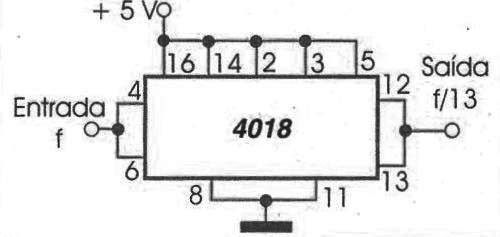

Divisor por 13

Para dividir por 13 temos um problema: não existem componentes TTL “fáceis” que podem fazer isso. Assim, um artifício que adotamos consiste em se usar um CMOS alimentado por 5 V. O CMOS admite sinais TTL na sua entrada e pode excitar entradas TTL com facilidade.

O circuito para a divisão por 13 emprega um contador base 16 4018 e é mostrado na figura 16.

A principal limitação existente neste circuito é que, com alimentação de 5 V, sua velocidade está limitada aos 4 MHz.

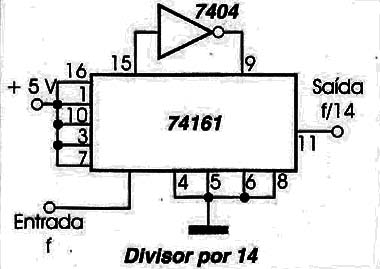

Divisor por 14

Para fazer a divisão por 14 além do contador base 16 74161 é preciso contar com a ajuda de um inversor externo, obtido num circuito integrado 7404. O divisor por 14 é mostrado na figura 17.

Para cada 14 pulsos de entrada obtemos um pulso de saída. Obtemos que o ciclo ativo não é 50% e que a velocidade máxima para o circuito TTL standard é de 25 MHz. Para maiores velocidades podem ser usados CIs das subfamílias TTL mais rápidas.

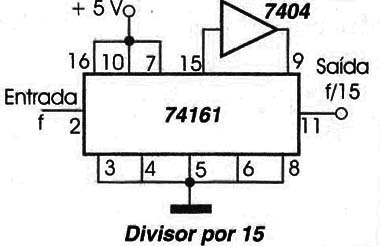

Divisor por 15

A divisão por 15 também pode ser feita com a ajuda de um 74161 mas precisamos de um inversor externo, obtido a partir de um circuito integrado 7404, conforme mostra a figura 18.

Os sinais obtidos na saída não têm um ciclo ativo de 50% e a freqüência máxima de entrada para a série standard é 25 MHz. CIs mais rápidos das subfamílias podem ser usados.

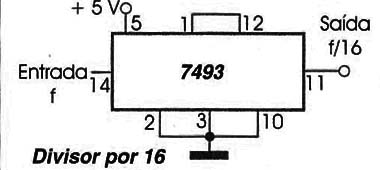

Divisor por 16

A divisão por 16 pode ser feita facilmente com um único circuito integrado 7493 que já consiste num contador/divisor base 16. O circuito é mostrado na figura 19.

A velocidade máxima para o sinal de entrada é de 18 MHz, mas CIs mais rápidos das subfamílias podem ser usados. Para cada 16 pulsos de entrada obtemos um pulso de saída.

A simulação no computador é mostrada para esse divisor.

Conclusão

As configurações que mostramos não são as únicas possíveis mas certamente estão entre as mais simples de implementar com componentes comuns.

Precisando de configurações que tenham características diferentes, tais como ciclos ativos de 50% ou ainda operação em modos específicos como sincronizado, ripple, etc., será conveniente consultar os manuais dos componentes usados e dos disponíveis para que as devidas alterações possam ser feitas.