Com o objetivo de facilitar a comunicação entre os circuitos em controles industriais, equipamentos de consumo e muitos outros tipos de aplicativos, a Philips lançou em 1992 um novo tipo de barramento que permitiu o uso de dois fios para a troca de informações de forma eficiente. O novo barramento, denominado Inter IC ou l2C, possibilita o uso de uma enorme variedade de componentes padronizados, que podem trocar dados de forma simples e eficiente. Tal foi o sucesso desse barramento que em pouco tempo ele se tornou um padrão mundial, um dos preferidos para as aplicações que envolvem todo o tipo de troca de dados entre circuitos utilizando cabos trançados. Esse sucesso levou ao aparecimento da versão 2.0, em 1998. O que é o I2C e como ele funciona, é o que veremos neste artigo de 2001.

A ideia básica do uso do barramento I2C é permitir a fácil integração em componentes de interface, que possam trabalhar diretamente com seus sinais simplificando assim a comunicação com outros componentes da mesma família.

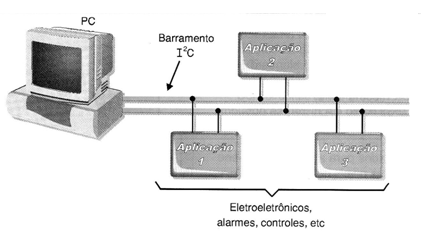

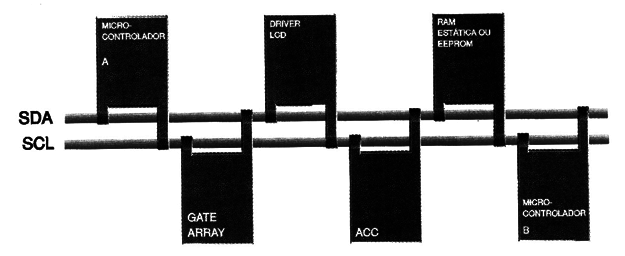

Na época que a Philips lançou este barramento, mais de 150 circuitos integrados ICMOS já eram compatíveis com ele. Veja a figura 1.

Para que os circuitos possam se comunicar de maneira eficiente, dentro da ideia básica do barramento I2C foi previsto que eles deveriam apresentar as seguintes características básicas:

Empregar apenas dois fios: uma serial data line (SDA) e uma serial clock line (SCL).

Cada dispositivo que fosse conectado ao barramento deveria ser endereçado por software com um único endereço, e relações simples entre mestre/escravo deveriam estar disponíveis o tempo todo.

No tipo final foram usados 10 bits para esse endereçamento.

Deveriam ser previstos recursos para detectar colisão de dados de modo a não haver dano aos dados transferidos em caso de transmissão simultânea.

Seriam utilizadas inicialmente velocidades de transferência de 100 kbits/s no modo standard ou 400 kbit/s no modo rápido.

Posteriormente, o low speed mode foi omitido.

Deveriam ser previstos circuitos de rejeição de picos e transientes on-chip para preservar a integridade dos dados.

O número de Cls conectados a um mesmo barramento seria limitado apenas pela capacitância máxima do barramento, de 400 pF.

A adoção deste padrão poderia facilitar em muito o projeto de equipamentos que precisam se comunicar com outros de forma simples e eficiente, uma vez que não seriam necessárias interfaces adicionais.

Mais do que isso, componentes de todos os tipos poderiam incorporar os circuitos de interface, o que significa que para interliga-los bastaria usar um par trançado sem a necessidade de circuitos de interface adicionais.

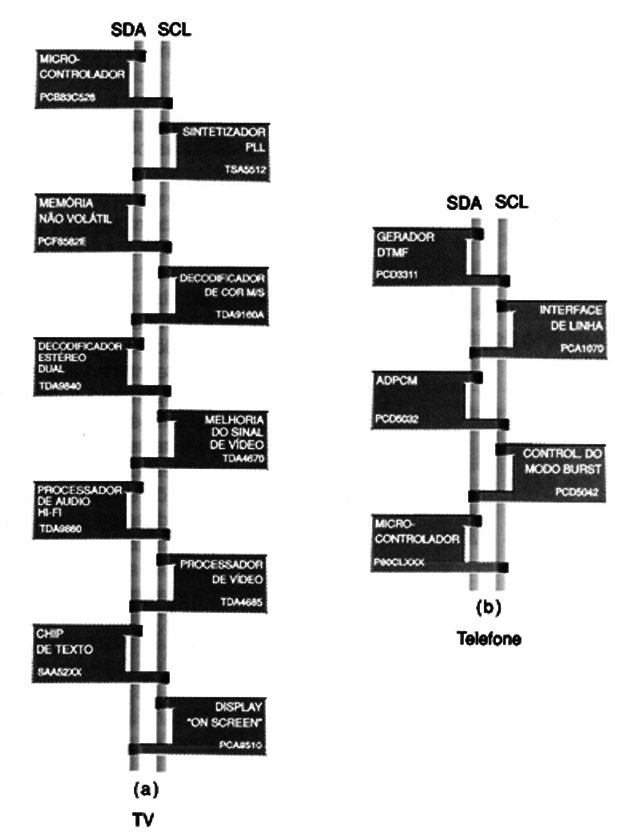

Na figura 2 temos exemplos de aplicação deste barramento num televisor altamente integrado para transferência de dados entre os diversos estágios.

Uma outra aplicação muito atraente está na utilização do PC como alternativa para aporta RS-232 na conexão de periféricos.

As ideias básicas das aplicações e da versatilidade de uso do barramento I2C foram mantidas, mas com a sua adoção como um padrão mundial com o licenciamento para seu emprego em mais de 50 empresas, alguns melhoramentos apareceram na versão 2.0, tais como:

Foi acrescentado o High-speed mode (Hs-mode) que permite uma transferência de dados a uma velocidade de até 3,4 Mbits/s. O interessante é que tanto os dispositivos rápidos como standard podem operar ao mesmo tempo pela mesma linha.

O nível baixo e a histerese dos dispositivos com tensão de alimentação de 2 V ou menos foram adaptados para atender as exigências dos níveis de ruído de modo a permanecerem compatíveis com os dispositivos de maior tensão de alimentação.

A exigência de 0,6 V sob 6 mA para as etapas de saída dos dispositivos de operação no Fast-mode foram omitidas.

Os níveis fixos de entrada para os novos dispositivos foram substituídos pelos níveis de tensão relacionados com o barramento.

O CONCEITO

Os barramentos I2C aceitam qualquer processo de fabricação de Cls (NMOS, CMOS, Bipolar, etc.), o que permite que dispositivos de qualquer tecnologia possam ter incorporados os circuitos deste barramento sem problemas, e que eles possam se comunicar sem conflitos.

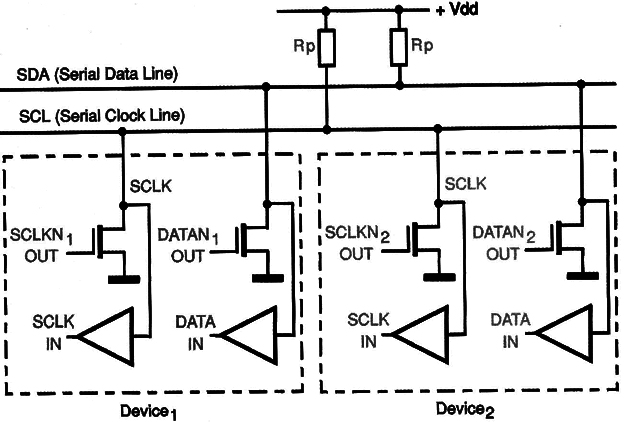

Dois fios de dados (serial data SDA e serial clock SCL) carregam as informações entre os dispositivos conectados ao barramento, conforme mostra a figura 3.

Cada dispositivo do barramento é reconhecido por um endereço único, mesmo que ele seja um microcontrolador, um LCD, uma memória ou uma interface de teclado, e pode operar como um receptor ou um transmissor de dados dependendo das suas funções.

Evidentemente, no caso mais simples que seria de um LCD, temos apenas um receptor que recebe os dados que deve apresentar a partir de um transmissor, enquanto que em outros como um teclado, por exemplo, pode tanto receber como enviar dados, pois precisa comunicar a um periférico a tecla pressionada e receber informações no momento em que é liberado ou que se espera que alguma determinada tecla seja ativada.

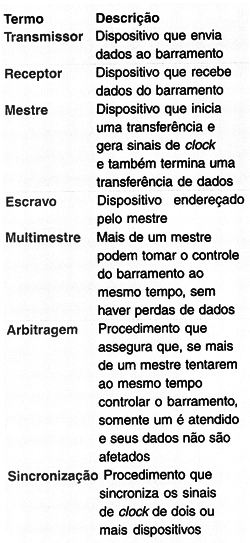

Os dispositivos conectados ao barramento podem ter diversas classificações, tais como mestres (MASTER) ou escravos (SLAVE), e algumas outras de acordo com a tabela a seguir:

Os dispositivos do Barramento FC

O barramento I2C é um barramento multimestre. Isso significa que mais de um dispositivo de controle pode ser conectado a ele. Na figura 4 temos um exemplo onde isso pode ocorrer.

Enquanto o microcontrolador 1 envia sinais ao driver LCD, o microcontrolador 2 troca informações com o microcontrolador 3 usando o mesmo barramento.

Para que os dados não sejam colocados simultaneamente no barramento, existe uma "arbitragem" que determina qual dos sinais tem prioridade no envio dos dados.

CARACTERÍSTlCAS ELÉTRlCAS

Tanto as linhas SDA como SCL são bidirecionais e devem ser ligadas ao positivo da alimentação através de uma fonte de corrente ou de um resistor pull-up, veja a figura 5.

Quando o barramento está livre, ambas as linhas permanecem no nível alto. Os dispositivos ligados ao barramento devem ter dreno aberto ou coletor aberto de modo a formar uma função AND.

Os dados são transferidos numa velocidade de 100 kbits/s ou 400 kbits/s no modo Standard ou 3,4 Mbits/s no modo High Speed.

O número de interfaces ligadas ao barramento dependerá somente da capacidade do mesmo de acordo com o indicado na parte inicial.

Como existem dispositivos de uma grande variedade de tecnologias que podem ser ligados ao barramento, os níveis baixo e alto (0 e 1) não são fixos e dependem apenas do nível associado de Vdd.

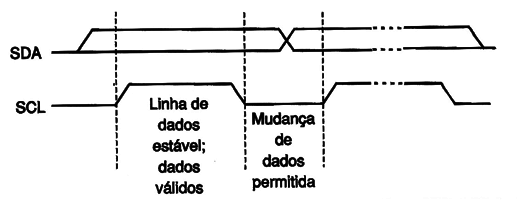

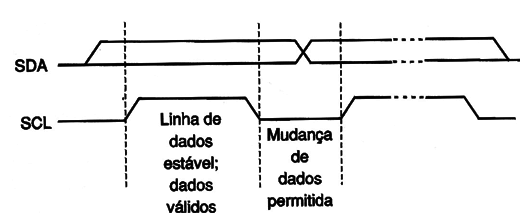

A cada pulso de clock um bit de dados é transferido.

Para que haja validade dos dados transferidos, a linha SDA precisa se manter estável durante o período em que o clock permanece no nível alto.

Os níveis alto ou baixo da linha de dados só podem mudar quando o sinal de clock na linha SCL estiver no nível baixo, conforme mostra o diagrama de tempos da figura 6.

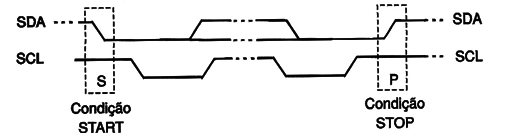

Na figura 7 temos um outro diagrama de tempos que mostra as condições de START e STOP.

Dentro da operação do barramento I2C temos os procedimentos START e STOP (S e P).

Uma transição do nível alto para o nível baixo na linha SDA enquanto a linha SCL está no nível alto, é um caso único que poderá ocorrer indicando uma situação de START.

Já uma transição do nível baixo para o nível alto na linha SDA enquanto a linha SCL se mantém no nível alto, define uma condição STOP.

Estas condições são geradas sempre pelo mestre. O barramento é considerado ocupado depois de uma condição START, e livre novamente algum tempo depois da condição STOP

Se forem geradas condições START seguidamente, o barramento se manterá ocupado.

Com circuitos apropriados pode-se implementar a função de detectar as condições START e STOP nos dispositivos que devem ser conectados ao barramento.

O FORMATO DO BYTE

Cada byte colocado na linha SDA deve ter 8 bits de comprimento.

O número de bytes que pode ser transferido em cada operação de transferência é ilimitado.

Cada byte tem apenas que ser seguido de um bit de reconhecimento.

Os bytes são transferidos de modo que o bit mais significativo MSB vai em primeiro lugar.

Se o dispositivo que está recebendo o sinal não puder manusear os dados recebidos, ele poderá alterar a linha SCL colocando-a no nível baixo de modo a forçar o mestre a entrar num estado de espera.

Somente quando a linha estiver novamente livre, a transferência de dados poderá continuar

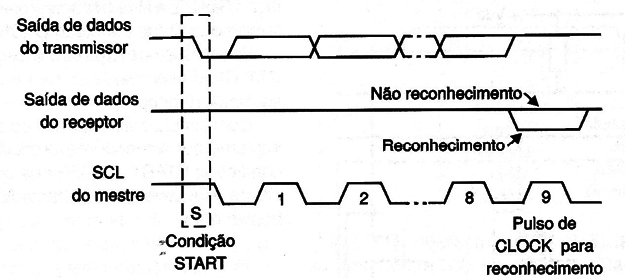

RECONHECIMENTO

O reconhecimento dos dados transferidos é obrigatório. O pulso gerado para esta finalidade é mostrado na figura abaixo.

O receptor tem a linha SDA colocada no nível baixo durante o pulso de clock de modo que ele permaneça estável no nível baixo durante o período alto do pulso de clock.

GERAÇÃO DE CLOCK E ARBITRAGEM

Como todas as unidades mestre geram seus próprios sinais de clock, na linha SCL existe o perigo destes pulsos afetarem a transferência de mensagem se misturados.

Para evitar isso, os dados são validados apenas no período em que o sinal de clock se encontra no nível alto.

Isso significa a necessidade de se ter uma arbitragem bit por bit.

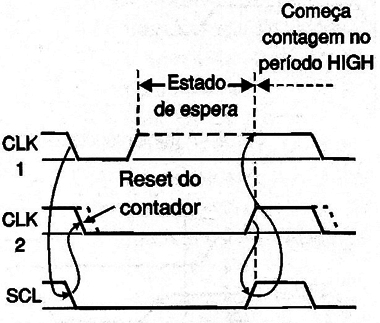

À sincronização dos clocks é feita através de portas AND nas interfaces do barramento.

Nelas, uma transição do nível alto para o nível baixo na linha SCL fará com que a contagem se inicie no período baixo e, uma vez que o clock de um dispositivo tenha ido ao nível baixo, ele manterá a linha SCL naquele estado até que um nível alto do clock seja alcançado, observe a figura abaixo.

Entretanto, a transição do nível baixo para o nível alto neste clock não fará com que ocorra mudança de estado na linha SCL, se outro clock ainda estiver no período de nível baixo.

A linha SCL será mantida no nível baixo pelo dispositivo que tenha o maior período no nível baixo.

Os dispositivos com períodos mais curtos no nível baixo entrarão num estado de espera no nível alto durante esse tempo.

Quando todos os dispositivos tiverem contado o seu tempo no nível baixo, o clock será liberado e irá ao nível alto.

Com isso, não ocorrerão diferenças entre os clocks dos dispositivos e o estado da linha SCL, e todos os dispositivos recomeçarão a contagem dos seus períodos no nível alto.

O primeiro dispositivo que completar seu tempo no nível alto colocará novamente a linha SCL no nível baixo.

Desta forma, um clock SCL sincronizado pode ser gerado através deste período baixo, determinado pelo dispositivo que tenha o período no nível baixo mais longo e seu período no nível alto será determinado pelo que tiver o tempo mais curto nesta situação.

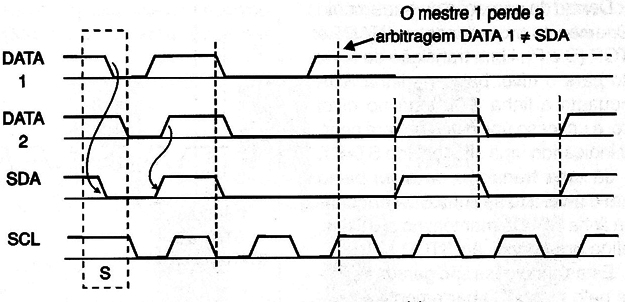

Um mestre deverá iniciar a transferência de dados somente se o barramento estiver livre.

Dois ou mais mestres devem gerar uma condição START, com o tempo máximo de manutenção da condição START resultando assim em uma condição definida de START no barramento.

A arbitragem ocorrerá na linha SDL no instante em que a linha SCL estiver no nível alto de tal forma que um mestre transmite o nível alto, enquanto aquele que estiver com a transmissão no nível baixo é desligado.

A arbitragem poderá continuar por diversos bits.

Seu primeiro estágio é a comparação dos bits de endereçamento.

Se os mestres estiverem cada um tentando endereçar o mesmo dispositivo, a arbitragem continuará com a comparação dos bits de dados verificando se eles são bits transmitidos ou de reconhecimento.

Na figura 11 mostramos as formas de sinais que ocorrem no processo de arbitragem que determina qual das transmissões prevalecerá numa transmissão de dados.

Observe que, uma vez que neste tipo de barramento o controle é decidido somente nos códigos de endereçamento do mestre e dados enviados pelos mestres, não existe um mestre central nem qualquer ordem de prioridade no barramento.

Um ponto importante para o qual deve ser chamada a atenção surge durante uma transferência de dados quando o procedimento de arbitragem ainda está ocorrendo no momento em que uma condição de START ou STOP é transmitida ao barramento.

Se tal situação acontecer, os mestres deverão enviar esta condição START ou STOP na mesma posição e formato.

FORMATOS DOS DADOS

Existem diversas possibilidades para a transmissão de dados. Veja a seguir:

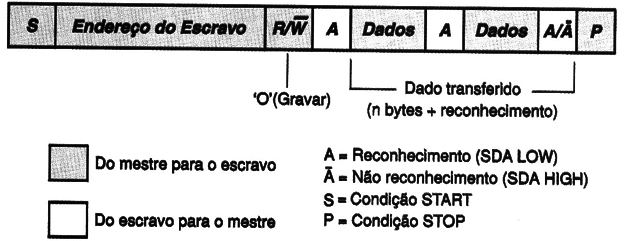

a) Em um primeiro formato, o transmissor mestre envia os sinais para um receptor escravo. Os sinais não têm o sentido de seu fluxo modificado. É a forma mais simples de transferência de dados. Conforme ilustra a figura 12.

b) Numa segunda possibilidade, o mestre faz uma leitura do escravo, imediatamente após o primeiro bit. No momento do primeiro reconhecimento, o transmissor mestre torna-se um receptor mestre e o receptor escravo torna-se um transmissor escravo. O primeiro reconhecimento é ainda gerado pelo escravo. A condição de STOP é gerada pelo mestre, que deve ter enviado previamente um sinal de não reconhecimento.

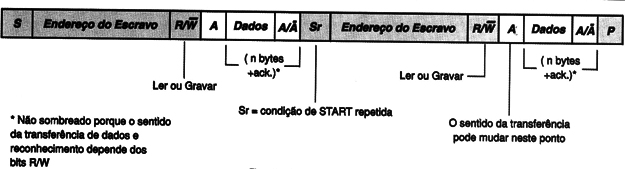

c) Um formato combinado é mostrado na figura 13.

Durante uma mudança de sentido do fluxo de sinais, com uma transferência a condição START e o endereço do escravo são ambos repetidos, mas com o bit R/\N invertido.

Se um receptor mestre envia uma condição START repetidamente, ele deve ter mandado previamente uma condição de não reconhecimento.

É importante observar que formatos combinados podem ser usados, e que todas as decisões sobre o autoincremento ou decremento das locações de memória acessadas além de outras características do sistema devem ser tomadas pelo projetista do dispositivo.