Nos últimos anos, a plataforma de desenvolvimento Arduino cresceu notavelmente. Isto ocorreu devido ao seu fácil manuseio, contribuições de hardware e software e interesse de empresas como Intel, Microsoft, Texas Instruments, etc., na adaptação de seus produtos a esta plataforma. Um das placas mais utilizadas é o Arduino Uno, cujo núcleo microcontrolador é o atmega328p. Neste artigo, conheceremos suas capacidades internas e arquitetura de microcontroladores, muito úteis ao projetar sistemas eletrônicos.

Alfonso Pérez

MIC019S MIC025E

A Figura 1 mostra a placa Arduino Uno, cujo hardware é aberto (aberto). Isso permite que muitas empresas de eletrônicos adaptem seus produtos a esta plataforma. Por exemplo, a Intel desenvolveu placas seguindo o Arduino Uno e usando alguns de seus processadores. A Texas Instruments desenvolveu placas seguindo Arduino Uno e usando alguns de seus microcontroladores. O IDE de desenvolvimento do Microsoft Visual Studio, permite que, por meio de um pacote de instalação, o código para Arduino possa ser editado. Assim, muitas empresas seguem o protótipo da Arduino. Daí a importância de conhecer este sistema e seu processador central, o ATmega328P. Este artigo mostra as principais características deste microcontrolador.

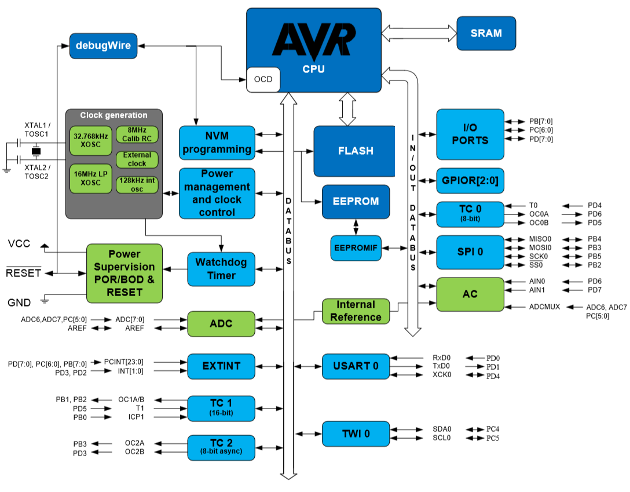

O ATmega328P é um microcontrolador de arquitetura avançada RISC AVR da Atmel, de alto desempenho, baixo consumo e otimizado para compiladores C. A Figura 2 mostra o diagrama de blocos do microcontrolador. Entre as principais características, podemos encontrar:

- 131 Instruções poderosas, a maioria executada em um único ciclo de relógio.

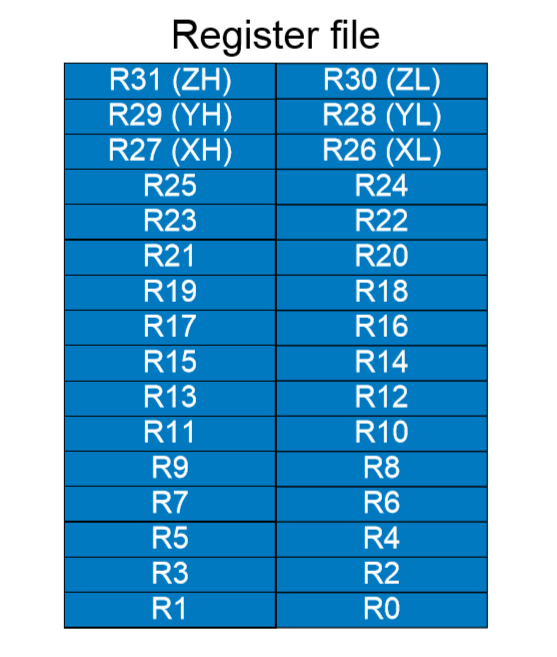

- Um banco de 32x8 registros de uso geral.

- Até 20 MIPS (Milhões de instruções por segundo) a 20 MHz.

- Um multiplicador de hardware on-chip de 2 ciclos.

- Memória de programa FLASH de 32 KB, programável dentro do sistema.

- Memória SRAM interna de 2 KBytes.

- Memória EEPROM de 1 KByte.

- 2 Temporizadores / Contadores de 8 bits.

- 1 Temporizador / Contador de 16 bits.

- 6 canais PWM.

- 6 canais analógicos para o ADC.

- 1 porta serial USART.

- 1 interface serial SPI.

- 1 interface serial de 2 fios, compatível com I2C.

- 1 temporizador de vigilância.

- 1 Um comparador analógico on-chip.

- Interrupções.

Vários modos de baixo consumo.

PINOS DO MICROCONTROLADOR ATmega328P.

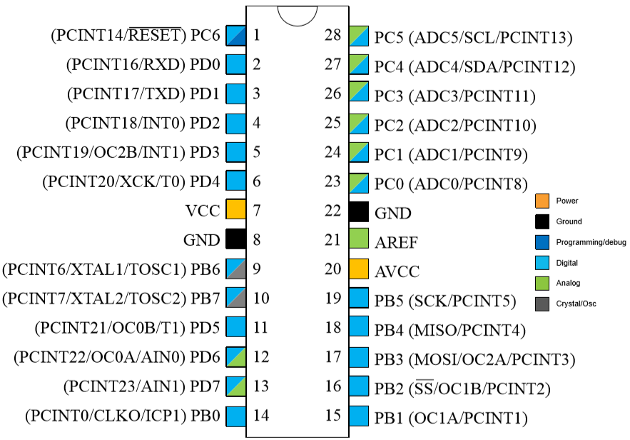

Na Figura 3 podemos ver as portas e os pinos de tensão. No total, existem 23 entradas / saídas programáveis, para uso geral (GPIO). Estes pinos também podem ser programados para funções alternativas, como comunicação serial, ADC, I2C, etc. A seguir estão as portas e os pinos principais do microcontrolador:

VCC: Tensão Digital.

GND: Terra.

PORTB: É uma porta bidirecional de 8 bits, com resistores pull-up internos, selecionáveis para cada pino. As funções alternativas para os pinos da PORTB são:

- XTAL

- SPI

- Comparadores de saída (Output Comapare) para temporizadores.

PORTC: É uma porta bidirecional de 7 bits, com resistores pull-up internos, selecionáveis para cada pino. As funções alternativas para os pinheiros

PORTC são:

- Entradas analógicas (ADC)

- I2C.

PORTD: É uma porta bidirecional de 8 bits, com resistores pull-up internos, selecionáveis para cada pino. As funções alternativas para os pinos PORTD são:

- porta serial do USART.

- Interrupções externas INT0 e INT1.

- Comparadores de saída para temporizadores.

AVcc: É o pino de tensão para o conversor analógico para digital (ADC).

AREF: pino de referência análogo para o ADC.

ARQUITETURA INTERNA DO MICROCONTROLADOR ATmega328P.

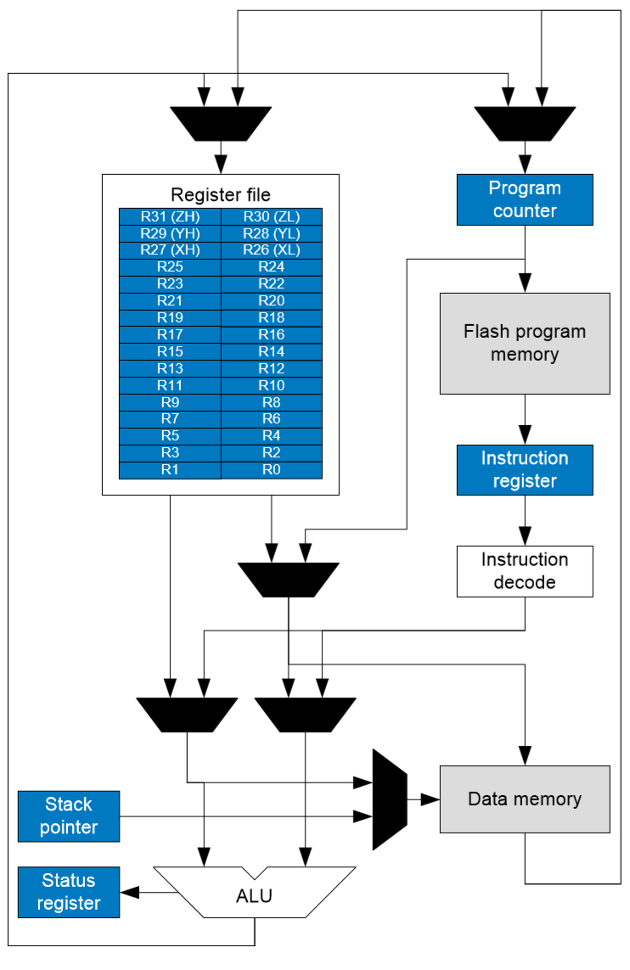

Na Figura 4 você pode ver o diagrama de blocos da arquitetura do microcontrolador ATmega328P. Este microcontrolador usa uma arquitetura Harvard, usando memórias e barramento separados para programas e dados. A CPU usa um pipeline (pipelining) de um nível, ou seja, enquanto está executando uma instrução, a próxima instrução está sendo pesquisada (pré-extraída) da memória do programa. Graças a esta técnica de pipeline e barramento separados, o microcontrolador pode executar as instruções em um único ciclo de clock.

O microcontrolador também possui um banco de registros de uso geral de 32 x 8 bits, com tempos de acesso de um único ciclo de clock. Isso permite que as instruções aritméticas e lógicas (ALU), possam ser realizadas em um único ciclo de relógio. Na Figura 5 você pode ver o banco de registros. Existem 6 registros que podem ser utilizados como 3 registros de endereços indiretos para a memória do programa, permitindo cálculos eficientes dos endereços na memória do programa, muito utilizados nos programas C. Estes registos são chamados X, Y, Z e utilizam os registros 26 a 31

MEMÓRIAS DO MICROCONTROLADOR ATmega328P.

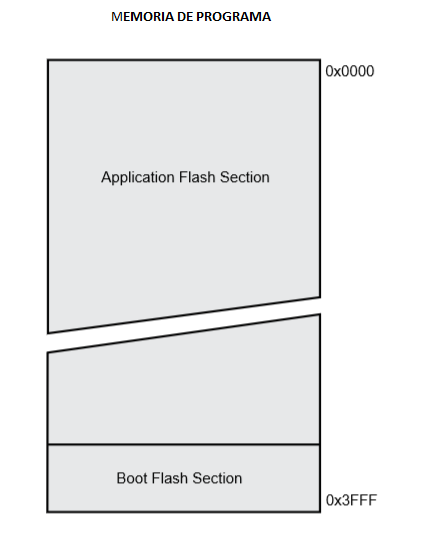

O microcontrolador ATmega328P tem uma memória Flash com 32 Kbytes reprogramável no sistema ou circuito, para o armazenamento do programa. Como todas as instruções AVR são 16 ou 32 bits, a memória Flash está organizada em 16K x 16. Para segurança do software, a memória Flash do programa é dividida em 2 espaços:

- A seção inicialização de inicialização (Boot Loader).

- A seção do programa da aplicação.

O contador do programa (PC) é de 14 bits, para que você possa abordar o 16K dos locais na memória do programa. A Figura 6 mostra o mapa de endereços para a memória Flash.

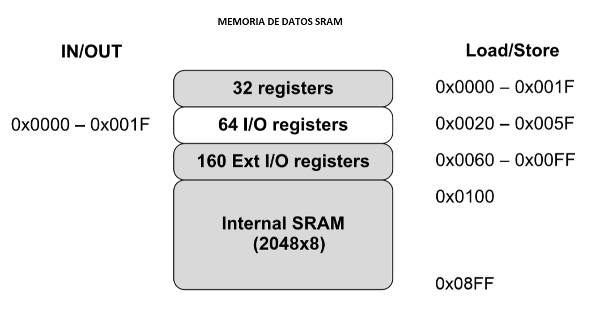

A memória SRAM (RAM estática) é formada por 2303 posições de memória. Na parte inferior estão: o banco (arquivo) de registros de uso geral, vindo então a memória de entradas / saídas, então, a memória de entradas / saídas estendidas e finalmente SRAM de dados. O banco de registro é de 32 bytes, a memória de entrada / saída é de 64 bytes, a memória de entrada / saída estendida é de 160 bytes e a SRAM de dados é de 2048 bytes. A Figura 7 mostra o mapa de memória para o SRAM. Essa memória pode ser abordada de 5 maneiras diferentes:

- Endereçamento direto.

- Endereçamento indireto com deslocamento.

- Endereçamento indireto.

- Endereçamento indireto com pré-decremento.

- Endereço indireto com pós-incremento.

Os 32 registros de uso geral, os 64 registros de entrada / saída, os 160 registros de entrada / saída estendidos e a SRAM interna de 2K são acessíveis através desses modos de endereçamento.

O microcontrolador possui uma memória EEPROM de 1 KB. É organizado como um espaço de memória separado, que pode ser lido ou escrito. A EEPROM permite 100.000 ciclos de gravação / apagamento.

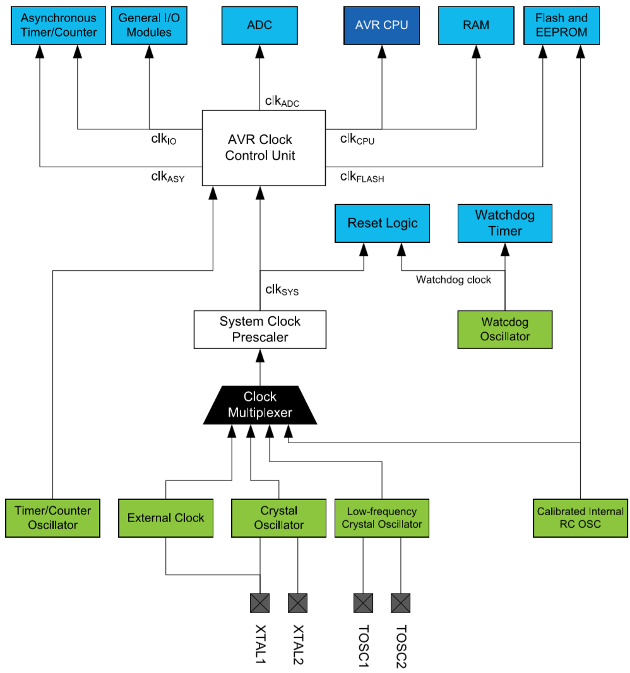

RELÓGIOS SYSTEMA (CLOCKS).

A Figura 8 ilustra os relógios do microcontrolador e sua distribuição. Não é necessário que todos os relógios estejam ativos no momento. Para reduzir o consumo, os módulos de relógio que não estão sendo usados ??podem ser interrompidos usando diferentes modos de baixo consumo.

O relógio da CPU é levado a partes do microcontrolador, em relação ao núcleo. Exemplos dessas partes são: Os 32 registros de uso geral, memória de dados, etc. O relógio de entrada / saída é usado por módulos como temporizadores / contadores, SPI, USART, interrupções externas, etc.

As fontes de relógio para o microcontrolador podem ser selecionadas a partir de um cristal de frequência externa baixa ou alta, um sinal de relógio digital externo ou um oscilador interno.

INTERRUPÇÕES NO ATmega328P.

Interrupções é o mecanismo de hardware pelo qual o microcontrolador descobre que há um evento urgente para participar. Para isso, o microcontrolador sai do programa principal e acompanha a interrupção, que é uma rotina de código para participar de um evento especial. Por exemplo, se houve uma mudança de estado em um pino, ou se um byte de dados chegou na porta serial, ou se um temporizador transbordou, ou se a conversão foi concluída no ADC, etc., estes são todos os casos típicos ou interrupções comuns que podem ser ativadas no microcontrolador.

As interrupções externas são acionadas pelos pinos INT0 ou INT1 e os pinos do PCINT. Podemos notar que mesmo que esses pinos estejam configurados como saída, a interrupção será desencadeada. Isso é muito útil ao gerar interrupções de software.

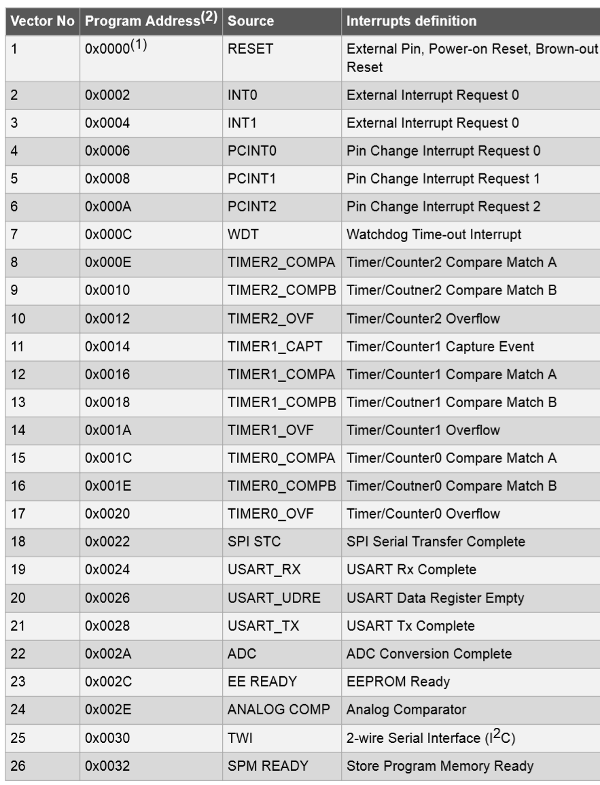

As interrupções externas podem ser desencadeadas pelo aumento da borda, ou queda da borda ou baixo nível. Essa configuração pode ser feita no registro de controle de interrupção externo (EICRA). A Figura 9 mostra a tabela de vetores de interrupção que o microcontrolador pode atender. Normalmente, é necessário ativar a interrupção com algum bit, em algum registro de controle. Para notificar que ocorreu um evento de interrupção, um bit (sinalizador) é definido como '1'. Quando a interrupção é atendida, este bit é automaticamente apagado por hardware.

(Portas de Entradas e daída) INPUT / OUTPUT PORTS

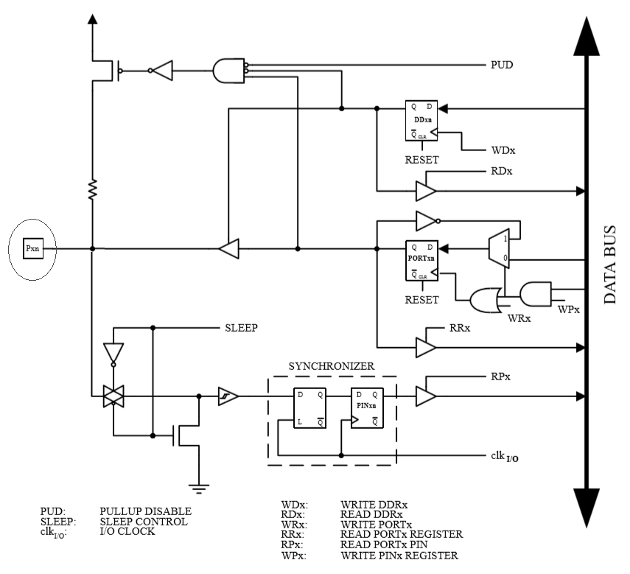

Todas as portas possuem funcionalidade read-modify-write quando usadas como pinos de entrada / saída. Isso significa que você pode alterar o valor de um bit sem modificar os outros, com as instruções Set Bit (SBI) e Clear Bit (CBI). A Figura 10 mostra a descrição funcional de um pino de entrada / saída do microcontrolador.

Cada pino de uma porta é composto por 3 bits. O DDxn no registro DDRx seleciona o endereço desse pino. Se DDxn for gravado em '1', o pino correspondente será configurado como saída. Se DDxn for gravado em '0', o pino correspondente será configurado como entrada.

Para gravar dados na porta, o registro PORTx é usado. Se PORTnx é escrito em '1', quando o pino é configurado como saída, o pino da porta é colocado em alto nível. Se PORTnx estiver escrito em '0', quando o pino é configurado como saída, o pino da porta é colocado em um nível baixo.

Se PORTnx estiver escrito em '1', quando o pino é configurado como entrada, o resistor de pull-up é ativado. Para desativar o resistor pull-up, o PORTnx deve ser gravado em '0' ou definir o pino como saída.

O registro PINnx é usado para ler o pino de porta.

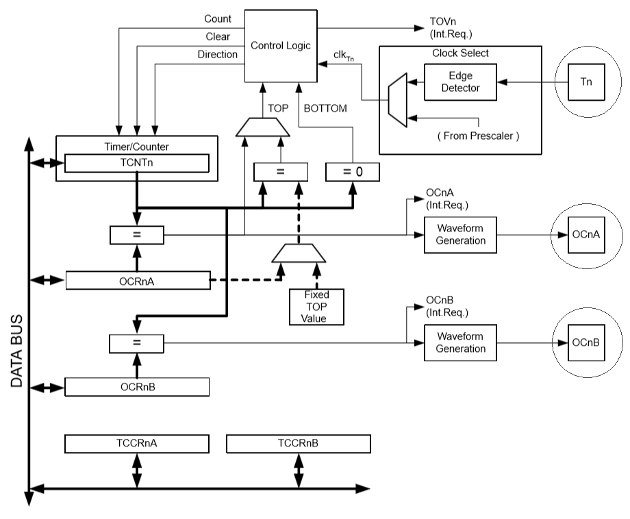

TC0 - TIMER / CONTADOR de 8-BIT Com PWM.

O Timer / Counter é um módulo para cronogramas e contagem de 8 bits de uso geral, com 2 unidades de comparação de saída e suporte para PWM. Assim, este módulo permite sincronizar com precisão a execução do programa e a geração de ondas.

Entre as principais características do TC0, estão:

- Possui 2 unidades independentes com comparadores de saída.

- Registra os comparadores de saída com 2 buffers.

- Clear no temporizador quando iguala à comparação (carga automática).

- PWM (Modulador de largura de pulso).

- Período PWM variável.

- Gerador de frequência.

A Figura 11 mostra o diagrama de bloco do Temporizador / Contador 0. A unidade do comparador de saída está verificando continuamente se o registro TCNT0 é igual aos registros OCR0A e OCR0B. Se TCNT0 for igual a OCR0A ou OCR0B, o comparador sinaliza uma igualdade, colocando a bandeira OCF0A ou OCF0B. Se a interrupção correspondente estiver ativada, a bandeira gerará uma interrupção da comparação de saída. O sinalizador é apagado automaticamente quando a interrupção é executada.

O temporizador / contador tem vários modos de operação. O modo normal é o mais simples. Neste modo, o contador está sempre ativo (incremento). Quando o contador atinge o valor programado, ele define para '1' a bandeira TOV1 de transbordamento (estouro) e, se ativado, pode gerar uma interrupção. Este sinalizador é apagado automaticamente quando a interrupção é executada.

O temporizador 0 e o temporizador 2 são 8 bits e as suas características são muito semelhantes. O temporizador 1 já possui 16 bits e tem o recurso de captura em uma de suas entradas. Isso é muito útil para medir a largura dos pulsos provenientes de algum circuito externo e assim medir distâncias ou frequências.

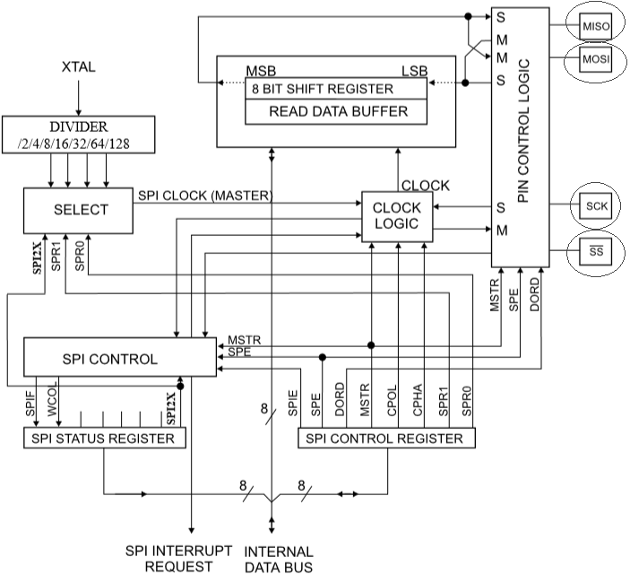

SPI - INTERFACE SERIAL DE PERIFÉRICOS.

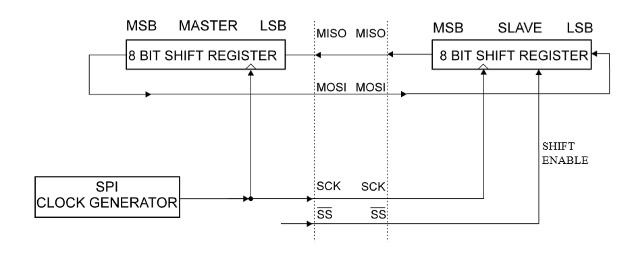

A interface periférica serial (SPI) permite a transferência de dados síncronos de alta velocidade entre o microcontrolador e as unidades periféricas. Na Figura 12 podemos ver o diagrama de blocos do SPI. A interconexão entre o mestre e o escravo é mostrada na figura 13. O sistema consiste em 2 registradores de deslocamento e um gerador de clock principal. O mestre inicializa a comunicação quando carrega o pino SS (Slave Selection) do escravo para o nível baixo '0', com o qual deseja se comunicar. O mestre e o escravo preparam seus dados para serem enviados em seus respectivos registros de deslocamento e o mestre gera os pulsos de clock necessários no pino SCK para troca de dados.

Os dados são movidos de Master para Slave na linha MOSI (Master Out - Slave In) e de Slave para Master na linha MISO (Master In - Slave Out). Depois de cada pacote de dados transferido, o Mestre sincroniza o escravo, levando o pino SS (Escravo) para o alto lógico '1'.

O periférico SPI é de um único buffer na direção da transmissão e com buffer duplo na direção da recepção. Isso significa que os bytes a serem transmitidos não podem ser gravados na gravação de dados SPI, antes que o ciclo de rolagem completo seja concluído. Ao receber dados, um caractere recebido deve ser lido a partir da gravação de dados SPI, antes que o próximo dado tenha sido completamente movido para dentro.

As principais características do SPI são:

- Duplex completo, transferências de dados síncronas com 3 linhas.

- Operações de mestre ou escravo.

- Transferência de dados LSB primeiro ou MSB primeiro.

- Geração de interrupção no final da transmissão.

- Proteção para colisão na gravação.

- Modo mestre de velocidade dupla CK / 2.

COMUNICAÇÃO SÉRIAL - USART (Transceptor de receptor assíncrono síncrono universal)

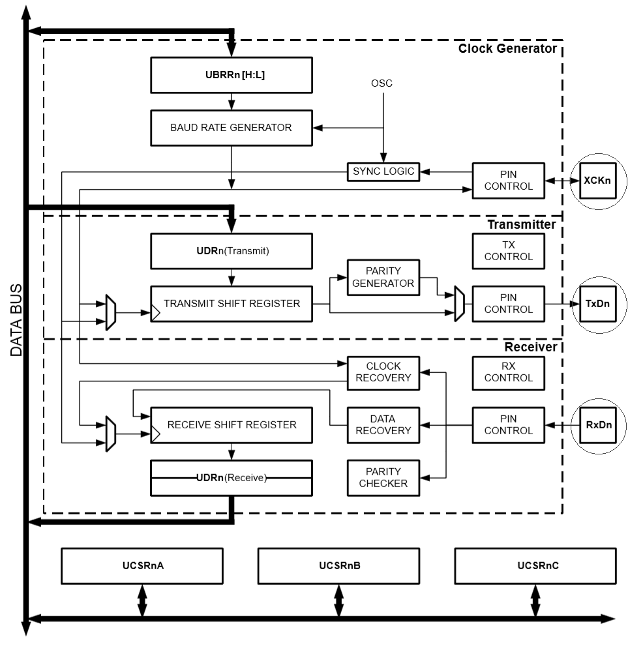

A USART é um periférico de comunicação serial altamente flexível. A Figura 14 mostra o diagrama de blocos da USART do microcontrolador. Na parte superior do diagrama de blocos, há o gerador do relógio, no meio é o transmissor e na parte inferior é o receptor. Esses blocos são separados por linhas pontilhadas ou descontinuados no diagrama de blocos. Os registros de controle são compartilhados por todos os blocos.

A geração de pulso consiste em: lógica de sincronização para entradas de relógio externas, usadas para operações com escravos síncronos e para gerar a velocidade de transmissão (taxa de transmissão). O pino XCKn é usado apenas por modos de transferência síncrona.

O transmissor consiste em: um único buffer de transmissão, um registro de deslocamento em série, um gerador de paridade e uma lógica de controle para lidar com diferentes formatos de dados em série (quadros). O buffer de gravação permite a transferência contínua de dados, sem qualquer atraso entre os quadros.

O receptor é a parte mais complexa do USART periférico, devido à sua unidade de recuperação de relógio e dados. A unidade de recuperação é usada para recepção de dados assíncronos. Além da unidade de recuperação, o receptor também possui um verificador de paridade, lógica de controle, um registro de deslocamento e um buffer de recebimento de nível 2 (UDRn). O receptor suporta o mesmo formato de quadros que o transmissor e pode detectar erros de dados (quadros), transbordamentos e erros de paridade.

Entre as principais características do USART, podemos encontrar:

- Operações full duplex (registros independentes para transmissão e recepção)

- Operações assíncronas e síncronas.

- Operações síncronas para comunicações Master Slave.

- Gerador de baud de alta resolução.

- Suporta quadros de dados em série de 5, 6, 7, 8 e 9 bits e 1 ou 2 bits de parada (parada).

- Gerador de paridade ímpar ou ímpar e verificação de paridade suportada por hardware.

- Detecção de excesso de dados.

- Detecção de erros nos quadros de dados.

- Inclui filtros de ruído.

- Modo de comunicação multiprocessador.

TWI - INTERFACE SERIAL DE 2 FIOS.

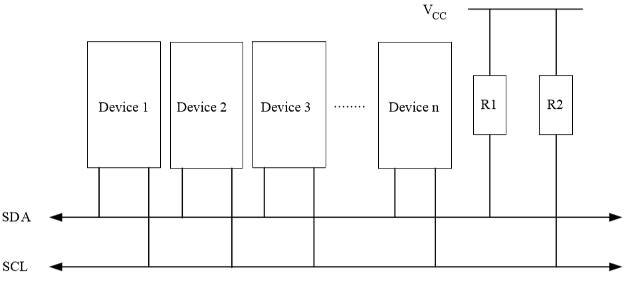

A Figura 15 mostra o protocolo TWI. O protocolo TWI (Interface de série de dois fios) permite a interconexão de até 128 dispositivos diferentes, usando apenas um barramento bidirecional de 2 linhas: SDA para dados e SCL para o relógio. O único hardware externo necessário para implementar o barramento é um único resistor para cada linha do barramento TWI. Todos os dispositivos conectados ao barramento possuem um endereço individual.

Cada bit de dados transferidos no barramento é acompanhado por um pulso na linha do clock. A única exceção a esta regra é gerar as condições start (START) e stop (STOP). O Mestre inicia e termina uma transmissão de dados. A transmissão é iniciada quando o mestre produz uma condição START no barramento e é encerrado quando o mestre emite uma condição STOP. Entre uma condição START e STOP, o barramento é considerado ocupado e nenhum outro mestre deve tentar controlar o barramento.

Todos os pacotes de endereços transmitidos no barramento TWI têm uma largura de 9 bits, consistindo de 7 bits para o endereço do escravo, 1 bit de controle para leitura / gravação e 1 bit de confirmação. Se o bit de leitura / gravação estiver configurado para '1' lógico, uma operação de leitura seria executada, se o bit estiver configurado para '0' lógico, então uma operação de gravação seria executada. Quando um dispositivo escravo reconhece que está sendo endereçado, ele deve reconhecer (ACK), carregando a linha SDA para baixo (baixa) no nono ciclo SCK. Então, o mestre pode transmitir uma condição STOP.

Todos os pacotes de dados têm uma largura de 9 bits, ocupa 8 bits para os dados e um bit de confirmação (ACK). Durante a transferência de dados, o mestre gera o relógio e as condições START e STOP, enquanto o receptor é responsável pelo reconhecimento (ACK).

Uma transmissão consiste basicamente em uma condição START, o endereço do escravo e se é lido ou escrito, um ou mais pacotes de dados e uma condição STOP.

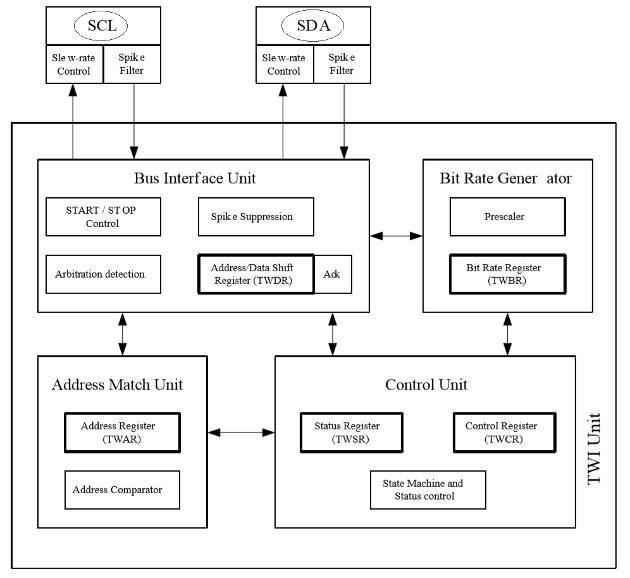

A Figura 16 mostra o diagrama de blocos do periférico TWI. Entre as principais características do periférico TWI, podemos encontrar:

- Interface de comunicação poderosa e flexível usando apenas 2 linhas.

- Suporta operações Master e Slave.

- O microcontrolador pode ser configurado como mestre ou escravo.

- Espaço de endereço de 7 bits, permite até 128 dispositivos diferentes.

- Suporte para gerenciar vários Mestres.

- Velocidades de transferência de 400 KHz.

- Circuitos de supressão de ruído.

- Compatível com o protocolo I2C da Phillips.

ADC - CONVERSOR ANALOGO PARA DIGITAL.

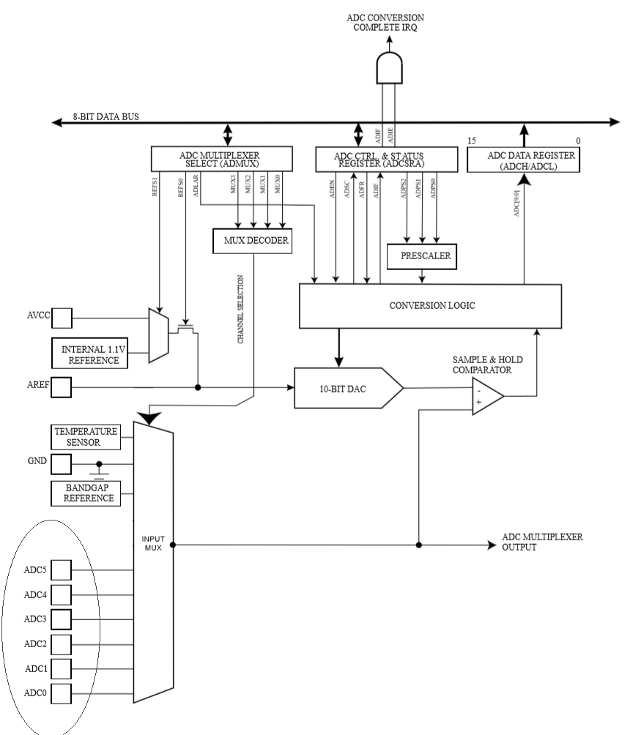

O microcontrolador possui um conversor analógico para digital de aproximação sucessiva de 10 bits. O ADC está conectado a um multiplexador analógico de 6 canais, permitindo fazer entradas de tensão, construídas nos pinos da porta C (PORTC). O ADC contém um circuito de amostragem e retenção garantindo que a entrada para o ADC seja mantida em um nível constante durante a conversão. A Figura 17 mostra o diagrama de blocos do ADC. O ADC possui um pino de alimentação de tensão separado chamado AVcc e não deve ser diferente de mais ou menos Vcc de 0,3 Volts.

O ADC converte uma entrada de tensão analógica para um valor digital de 10 bits através de aproximações sucessivas. O valor mínimo é representado pelo GND e o valor máximo representa a tensão no pino AREF. Opcionalmente, AVcc ou uma tensão de referência interna de 1.1 Volts, podem ser conectados ao pino AREF. A tensão de referência interna deve ser desacoplada por um capacitor externo no pino AREF para melhorar a imunidade ao ruído.

O canal de entrada analógica é selecionado por escrito nos bits MUX no Multiplexer Selection Register (ADMUX.MUX [0: 3]). Qualquer entrada analógica, bem como GND e uma tensão de referência fixa, podem ser selecionados como entrada para o ADC. O ADC gera um resultado de 10 bits, que é representado nos registros de dados do ADC (ADCH e ADCL). Por padrão, o resultado é ajustado para a direita, mas pode ser opcionalmente representado à esquerda, definindo o bit de ajuste à esquerda do ADC (ADMUX.ADLAR) para '1'. O ADC tem sua própria interrupção, que pode ser gerada quando uma conversão é concluída.

Para inicializar uma conversão, o bit de redução do consumo deve ser gravado em '0' no Registro de Redução de Consumo (PRR.PRADC) e gravar para '1' o bit de início da conversão do ADC localizado no registro do Controle A. Status ADC (ADCSRA.ADSC). O bit ADSC permanecerá alto, desde que a conversão esteja em andamento e será limpa pelo hardware, quando a conversão estiver concluída. Por padrão, o circuito de aproximação sucessiva requer uma entrada de frequência de clock entre 50 KHz e 200 KHz para alcançar a resolução máxima.

As principais características do ADC são:

- Resolução de 10 bits.

- Tempos de conversão entre 13 e 260 segundos micro.

- 6 canais de entrada multiplexados.

- Canal de entrada com sensor de temperatura.

- Ajuste de leitura opcional para a esquerda.

- Faixa de tensão de 0 a Vcc.

- Tensão de referência de 1.1 Volt para o ADC.

- Modo de conversão simples ou livre.

- Interrupção quando a conversão é concluída.

- Cancelamento de ruído em modo de baixo consumo (SLEEP).

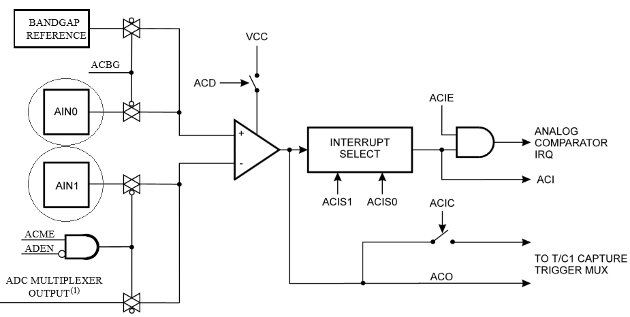

AC - COMPARADOR ANALOGO.

O comparador analógico compara os valores de entrada no pino positivo AIN0 e no pino negativo AIN1. Quando a tensão no pino positivo AIN0 é superior à tensão no pino negativo AIN0, a saída do comparador analógico (ACO) é ajustada para "1". Esta saída pode ser usada para disparar a função de captura do temporizador / contador 1. Além disso, o comparador analógico pode desencadear uma interrupção separada. O usuário pode escolher o disparo da interrupção de saída do comparador quando o bit ACO subir, diminuir ou mudar seu estado (alternar). A Figura 18 mostra o diagrama de blocos do comparador analógico.

Onde Comprar: